# TOWARD A FLIP-CHIP BONDER DEDICATED TO DIRECT BONDING FOR PRODUCTION ENVIRONMENT

Pascal Metzger, Nicolas Raynaud: SET

A. Jouve, N. Bresson, L. Sanchez,

F. Fournel, S. Cheramy:

**CEA-Leti**

# **Agenda**

- Introduction

- Process and Tool description

- Die-to-Wafer direct bonding process

- Tool overview

- Bonding tool performances evaluation

- Particle contamination

- Alignment accuracy

- Equipment throughput

- Application on oxide/oxide direct bonding

- Conclusion

#### Introduction

- Fine Pitch and High Throughput

- Challenges of microbumps technology

- Undercut

- Microbridging

- Assets of Direct Bonding

- Short process time

- Bonding (and alignment) at room temperature

- Low force

- D2W vs W2W

- Good yield (KGD)

- Heterogeneity of dies (type, size, thickness...)

- Challenge of cleanliness

# Fine pitch comparison process only - Trend

Need of Pre-applied underfill – Planarization – Cost Expensive flip-chip – Risk of microbridging and lateral overetch Cu-Cu C2W Cu-Cu W2W Area where Hybrid Bonding starts to be cost effective Copper pillar chip-to-chip Comparative data only or chip-to-wafer 1µm 10µm 25µm **Pitch**

# **Die-to-Wafer** W2W bonding flow direct bonding process

Top & Bottom wafers

#### Die-to-Wafer bonding flow

Top die

2. Top die dicing

3. Holder placement

Bottom wafer

2.Plasma activation (optionnal)

5. Die-to-Wafer stacking

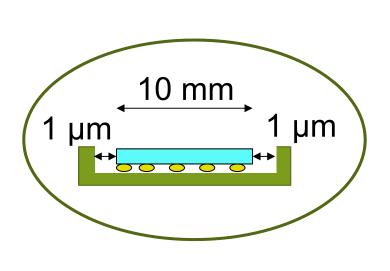

# Two antinomic specifications | Wafer-Level Packaging Conference

# Main targets

Precision: ± 1 μm

Throughput: 1000 dph

1700 mm

### **Tool overview**

# Main targets

Precision: ± 1 μm

Throughput: 1000 dph

High cleanliness

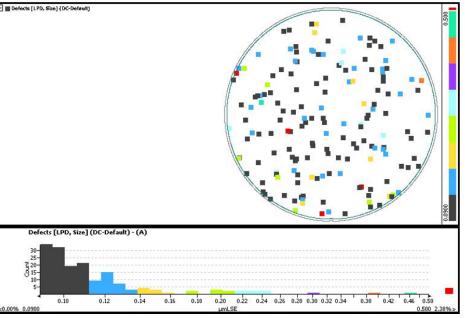

#### **Particle contamination**

#### Method

- Measurement of number of particles on wafers

- Just after cleaning

- After running tests under various conditions

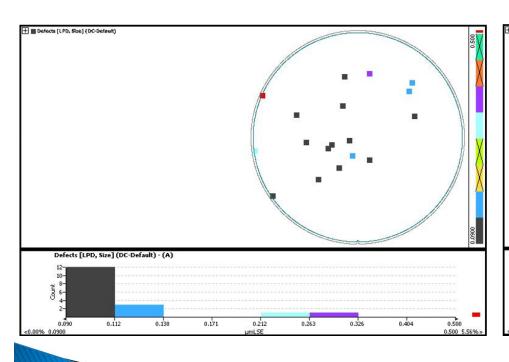

### **Particle contamination**

- One example: Influence of Y axis

- Theoretical throughput = 1000 dph

- Low level of contamination = 150 added particles in 1 hour

#### **Particle contamination**

- Synthetic results table

- Acceptable level of contamination for the process

- Nevertheless, continuous corrective actions plan on feeder

| COMPARISON BETWEEN NUMBER OF PARTICLES |           |           |       |         |  |  |  |  |  |

|----------------------------------------|-----------|-----------|-------|---------|--|--|--|--|--|

| Particle size                          | Reference |           |       | Support |  |  |  |  |  |

| [nm]                                   | Wafer     | Cleanroom | Chuck | Holder  |  |  |  |  |  |

| Box#                                   | 1         | 4         | 7     | 10      |  |  |  |  |  |

| Initial (just after cleaning)          |           |           |       |         |  |  |  |  |  |

| 90-500                                 | 13        | 43        | 17    | 19      |  |  |  |  |  |

| > 500                                  | 0         | 1         | 1     | 0       |  |  |  |  |  |

| After test (added particles)           |           |           |       |         |  |  |  |  |  |

| 90-500                                 | 200       | 121       | 147   | 322     |  |  |  |  |  |

| > 500                                  | 16        | 5         | 3     | 67      |  |  |  |  |  |

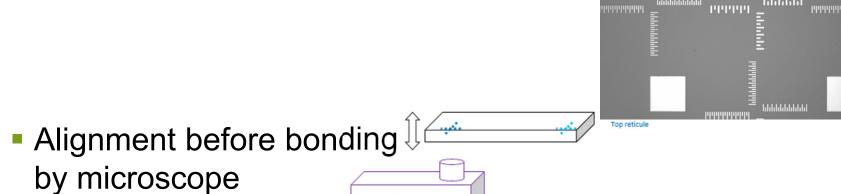

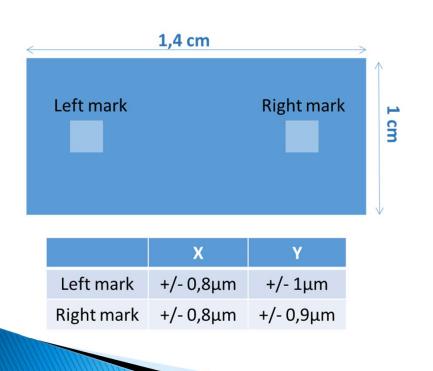

# Alignment accuracy

Transparent reticles

Check post-bond accuracy by microscope

# **Alignment accuracy**

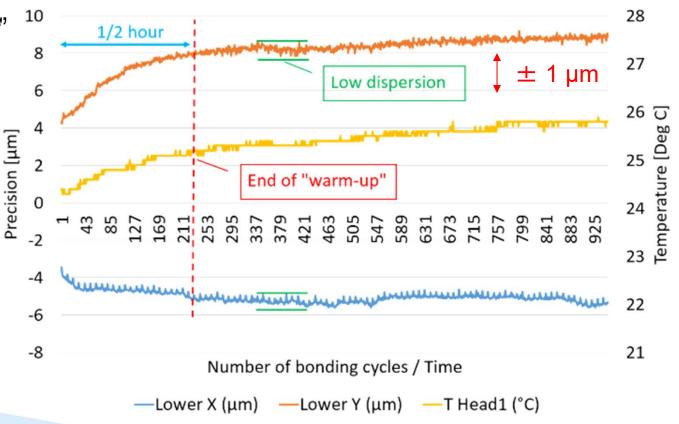

# Repeatability

- 1 position = Center of wafer

- Low dispersion

- "Warm-up time"

Bonding HEAD at the same position - Throughput 500 DPH

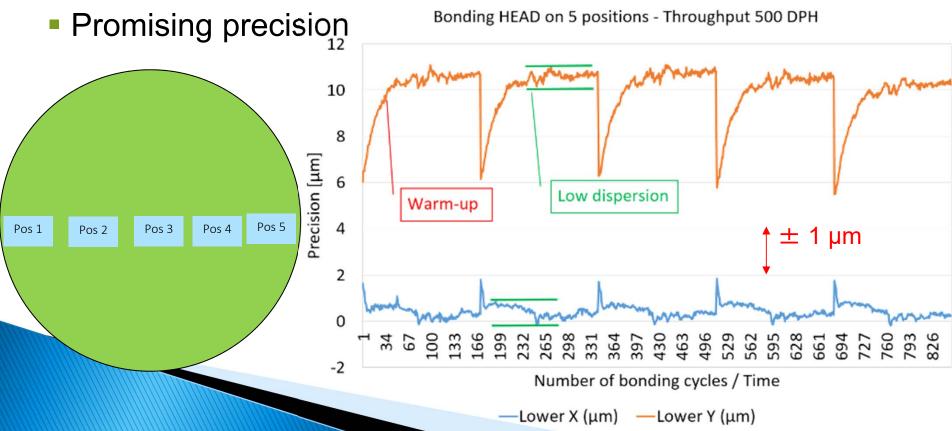

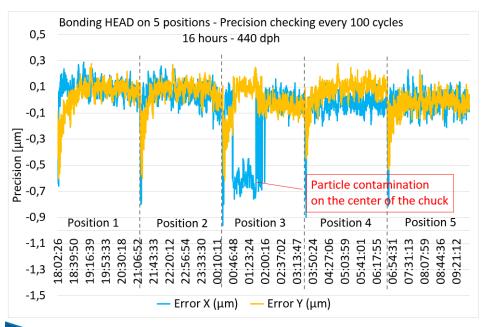

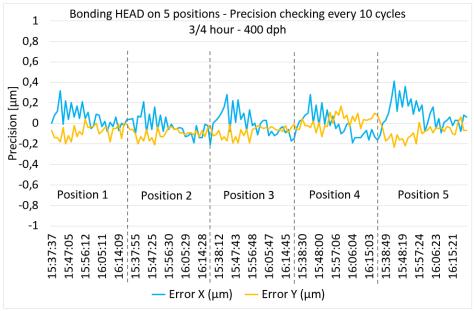

# **Alignment accuracy**

- Repeatability

- 5 positions = on Diameter of wafer

- Low dispersion

- "Warm-up time"

# **Equipment throughput**

- Theoretical throughput = 900 dph

- Elementary steps

- Hidden time / in sequence

|                          |                                                       | Time in | 1           |            |              |            |

|--------------------------|-------------------------------------------------------|---------|-------------|------------|--------------|------------|

|                          |                                                       | sec     | 1 Cell= 0.5 | 5 s        |              |            |

|                          |                                                       |         |             |            |              |            |

|                          | Load Chip Magazine (Align + Pick On Magazine -> Head) | 1       | 4s          |            |              | 4s         |

| d1                       | Go In Alignment Position XYTheta, Z Focus + XY Optic  |         | 15          | <b>1</b> s |              | 1s         |

| Неа                      | Move Optic In Alignment position                      |         |             | <b>1</b> s |              |            |

| Ĭ                        | Ă Alignment H1                                        |         |             | 1,59       | 5            |            |

|                          | Placement H1                                          | 1,5     |             |            | <b>1,5</b> s |            |

| ead2                     | Load Chip Magazine (Align + Pick On Magazine -> Head) | 4       |             | 4s         |              | Н          |

|                          | Go In Alignment Position XYTheta, Z Focus             | 1       | 1s          | <b>1</b> s |              | 1s         |

|                          | Move Optic In Alignment position                      | 0       | 1s          |            |              | <b>1</b> s |

|                          | Alignment H2                                          | 1,5     | 1,5s        |            |              |            |

|                          | Placement H2                                          | 1,5     | 1,          | 5s         |              |            |

|                          |                                                       |         |             |            |              |            |

| Number of Heads          |                                                       | 2       | Heads       |            |              |            |

| Cycle time for 1 Head =  |                                                       | 8       | s / die     | 1 cycle    |              |            |

| Throughput for 1 Head =  |                                                       | 450     | DPH         |            |              |            |

| Throughput for 2 Heads = |                                                       | 900     | DPH         |            |              |            |

# **Equipment throughput**

- Throughput vs Accuracy

- Trade-off

- Promising Throughput and Precision

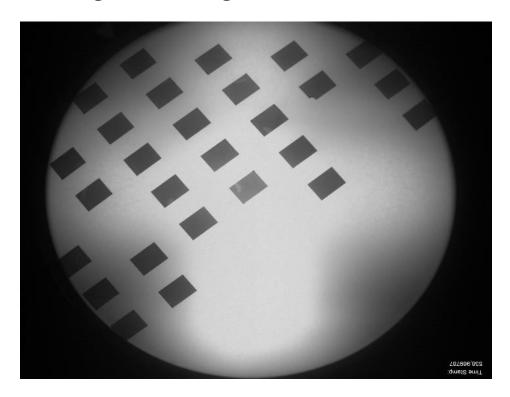

# Application on oxide/oxide direct bonding

#### Conditions

- 1 x 1,4 mm² dies with 2 verniers

- 750 nm of TEOS oxide

- CMP + dicing

- 28 dies on Ø 200 mm wafer

- 450 dph

# Application on oxide/oxide direct bonding

#### Results

Process in line with direct bonding challenges

### Conclusion

### Main targets

Precision

Throughput

High cleanliness

→ Dispersion < ± 0,25 µm

→ Post-bond accuracy < ± 1 µm</p>

→ ≈ 500 dph

Acceptable level

→ Actions on progress

#### Future work

- Continue qualification of beta tool

- Harvest measurements on precision, throughput, cleanliness

- Qualify the process on active device, full morphological and electrical characterization

- Demonstration on customers components possible in 2018

# Thank you for your attention!

Warms thanks to CEA-Leti team and SET team

This work was funded thanks to the French national program "Programme d'investissements d'Avenir,

IRT Nanoelec" ANR-I0-AIRT-05".

leti

MINATEC Campus, 17 rue des Martyrs, 38054 Grenoble, France

www.leti.fr

131 impasse Barteudet, 74490 Saint-Jeoire, France

PMetzger@set-sas.fr

www.set-sas.fr