# **SET Technical Bulletin**

# **DIE BONDING APPLICATIONS**

- An Innovative Die to Wafer 3D Integration Scheme: Die to Wafer Oxide or Copper Direct Bonding with Planarised Oxide Inter-Die Filling

- RF MEMS and Flip-Chip for Space Flight Demonstrator

- Electrically Yielding Collective Hybrid Bonding for 3D Stacking of ICs

- A Fluxless Bonding Process using AuSn or Indium for a Miniaturized Hermetic Package

- High Density Cu-Sn TLP Bonding for 3D Integration

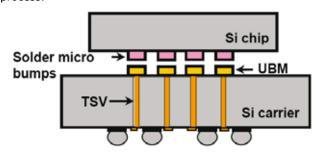

- Three Dimensional Interconnects with High Aspect Ratio TSVs and Fine Pitch Solder Microbumps

- High Density Cu-Cu Interconnect Bonding for 3-D Integration

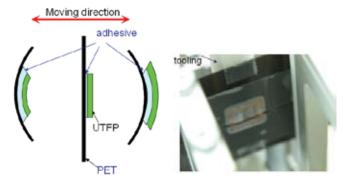

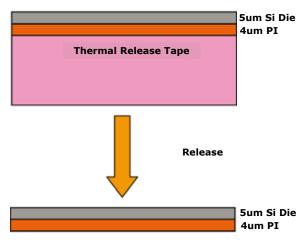

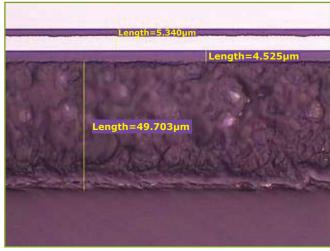

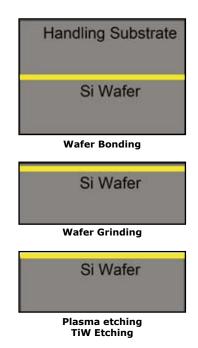

- Manufacturing & Stacking of Ultra-Thin Film Packages

- New Reflow Soldering and Tip in Buried Box (TB2) Techniques for Ultrafine Pitch Megapixels Imaging Array

- Electrical Characterization of High Count, 10 μm Pitch, Room-Temperature Vertical Interconnections

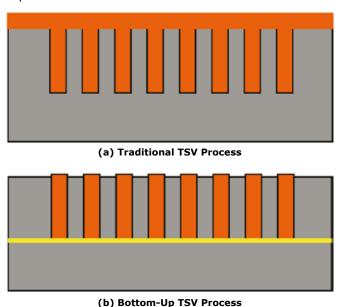

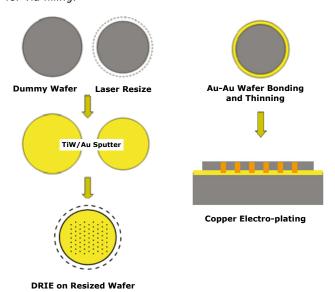

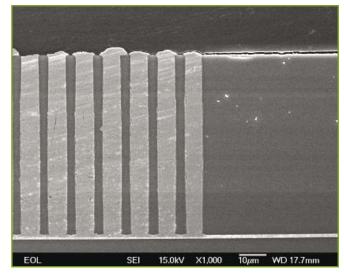

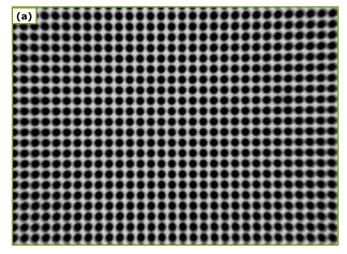

- 3D Stacked Chip Technology Using Bottom-up Electroplated TSVs

- Study of 15µm Pitch Solder Microbumps for 3D-IC Integration

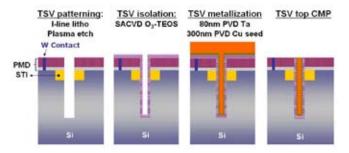

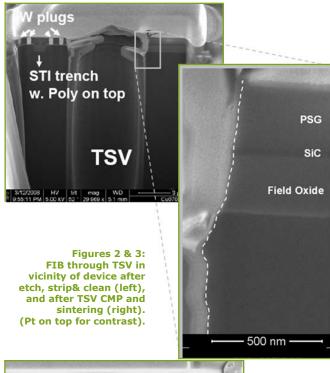

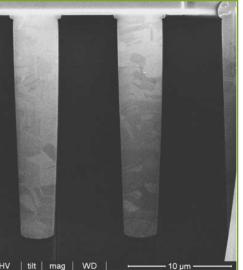

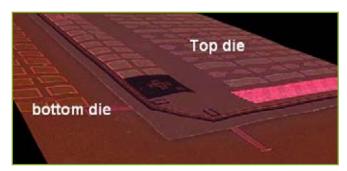

- 3D Stacked IC Demonstration using a Through Silicon Via First Approach

# TABLE OF CONTENTS SET is well Positioned and Prepared to address the Challenges of the fast growing 3D System Integration Market An Innovative Die to Wafer 3D Integration Scheme: Die to Wafer Oxide 6 or Copper Direct Bonding with Planarised Oxide Inter-Die Filling..... RF MEMS and Flip-Chip for Space Flight Demonstrator.... .10 14 Electrically Yielding Collective Hybrid Bonding for 3D Stacking of ICs High Density Cu-Sn TLP Bonding for 3D Integration 26 Three Dimensional Interconnects with High Aspect Ratio TSVs and Fine Pitch Solder Microbumps... 32 High Density Cu-Cu Interconnect Bonding for 3-D Integration 38 Manufacturing & Stacking of Ultra-Thin Film Packages. .43 New Reflow Soldering and Tip in Buried Box (TB2) Techniques for Ultrafine Pitch Megapixels Imaging Array 50 Electrical Characterization of High Count, 10 µm Pitch, Room-Temperature **Vertical Interconnections** 58 3D Stacked Chip Technology Using Bottom-up Electroplated TSVs 64 Study of 15µm Pitch Solder Microbumps for 3D-IC Integration .71 3D Stacked IC Demonstration using a Through Silicon Via First Approach 76 High Density 3D Interconnection 80

Since the advent of photolithography in electronics in the early sixties, and for decades, most new technology developments for the semiconductor industry have aimed at downsizing the transistors so as to make more integrated, more powerful, faster and even cheaper Integrated Circuits (ICs). Since a few years, this industry has changed and this in turn shifted the paradigm of technology innovation for semiconductors: a consensus is rising within the community of process experts and scientists that further downsizing of the transistors will not only become more difficult because new geometries tend to the physical limit of atom sizes, but it will also come along with lower performance side-effects such as higher parasitic coupling, higher current leakage and thermal issues. From an investors' perspective, the math is simple: in order to reach the next CMOS technology node, huge investments are needed, and the expected benefits are still unclear.

In parallel, electronic applications are being thought differently and processing power is now less seen as an end than as a means to develop and build user-friendly communica-

ting personal devices and appliances. You do not only want a game console with bright and fast high resolution graphics. You now want to interact with it: it can feel and sense you in every possible way, by means of motion and video sensors. Patients with cardiac rhythm malfunctions want to enjoy their lives as they did before being equipped with a pacemaker: continuous monitoring is now made possible as the pacemaker device measures the heart beats and directly sends relevant information via the patients cell phone to his physician without requiring any formal examination at the doctor's. As a consequence, there is rising awareness that integrated circuits are increasingly interacting with the real world by receiving, processing and transmitting more information than ever before. The focus is shifting from the transistors constituting the integrated circuits to their external interfaces, from processors to sensors and actuators, from circuits to systems: the value of semiconductors is shifting from ICs to IC and system packaging.

But the challenges remain the same ones as 50 years ago: how to make high performance, fast, low consumption and

# 3D TSV Packaging Market Value Forecast

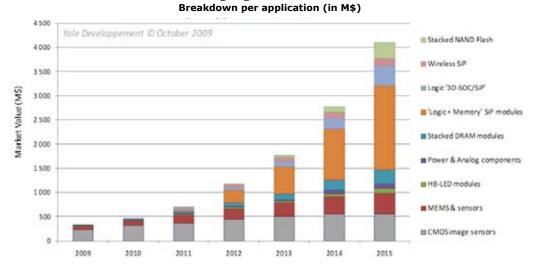

Figure 1 - 3D TSV Packaging Market Value Forecast: Breakdown per application (in M\$).

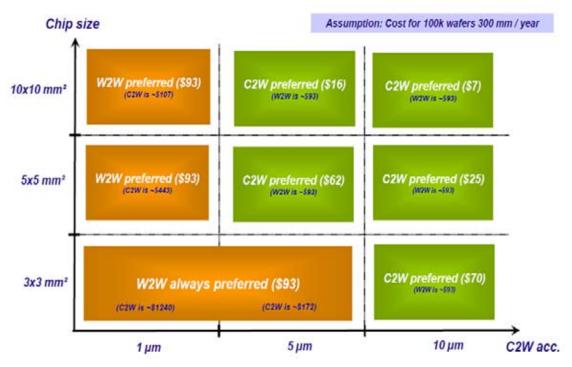

Figure 2 - Cost effectiveness of bonding scenarii function of die size and needed placement accuracy.

cheap highly integrated electronic systems? What is changing is how this is now increasingly being addressed. And the answer stands in a few keywords: mid-end, wafer-level packaging, 3D integration. The whole idea is to pack more electronic function per volume unit (instead of surface area) and to extend the photolithography techniques beyond the making of ICs to their packaging and their integration in a system. And this is a heavy trend: Yole forecasts that from slightly less than M\$ 500 in 2010, the market of 3D integration using through silicon vias (TSV) will grow to more than D\$ 4 in 2015 (figure 1), addressing a wide variety of advanced systems! Packaging of MEMS and sensors using wafer-level techniques will become mainstream in just a few years as we forecast a compound annual growth rate of 85% over the 2009-2013 time period!

Ahead of time of the other players in the value chain of the semiconductor industry, equipment manufacturers are bound to play an important role so as to tackle the technology challenges and seize the opportunities offered by this paradigm shift. SET demonstrated throughout this technical bulletin their active involvement in each and every area of technology innovation resulting from this industry trend. All the technical articles in this bulletin either deal with 3D integration of integrated circuits or packaging of MEMS and sensors using wafer level techniques, and all of them demonstrate how the SET bonders can be adequately used with varying process parameters: die to die bonding or die to wafer bonding, copper tin or gold tin or solder alloys, with flux or flux-less, with a wide range of die and wafer thicknesses, within front-end or back-end factory environments.

Thanks to the equipment flexibility, recipes combining the right placement accuracy, compression duration, force and temperature can be defined to meet the requirements of bonding strength and reliability with high industrial throughput.

Moreover, SET is well-positioned on the die to die (or chip to chip) and especially on the die to wafer (or chip to wafer) bonders which represent the favorite solution for a vast majority of industrials. Indeed, the chip to wafer bonding technique already allows better costs than "chip to chip" as it enables batch processing at the wafer level. On the other hand, it offers more integration flexibility than wafer to wafer as different size ICs using heterogeneous wafer processes can be stacked using chip to wafer. It is also clear that by choosing the chip to wafer bonding option, the bonded chips can be pre-tested, and only good ICs are reported on the host wafer allowing for much higher stack yields than when using wafer to wafer. This accounts for the cost competitiveness of the chip to wafer bonding technique served by SET versus the wafer to wafer bonding technique for many given configurations of die sizes and required placement accuracies as illustrated in figure 2.

SET clearly appears to be well positioned and prepared and with the right focus to address any new opportunity offered by the high growth mid-end semiconductor market of 3D system integration.

# An Innovative Die to Wafer 3D Integration Scheme: Die to Wafer Oxide or Copper Direct Bonding with Planarised Oxide Inter-Die Filling Léa Di Cioccio\*, Pierric Gueguen\*, Laurent Clavelier\*, Thomas Signamarcheix\*, Laurent Bally\*, Laurent Vandroux\*, Marc Zussy\*, Sophie Verrun\*, Jérôme Dechamp\*, Patrick Leduc\*, Myriam Assous\*, David Bouchu\*, François de Crecy\*, Laurent-Luc Chapelon\*, Rachid Taibi\*. \*-CEA/Leti-Minatec, 17 rue des Martyrs, F-38054 Grenoble Cedex 9, France \*-STMicroelectronics, 850 rue Jean Monnet, 38920 Crolles Cedex - France \*e-mail: lea.dicioccio@cea.fr

Copyright © 2009 IEEE. Reprinted from IEEE 3DIC 2009 proceedings.

### **ABSTRACT**

An innovative die to wafer stacking is proposed for 3D devices. Known good-dice are bonded on a processed wafer thanks to direct bonding. Oxide layers or patterned oxide/copper layers are used as the bonding medium. After a first thinning, a low stress high deposition rate oxide is deposited to embed the dice. A final thinning is then done to recover a flat and smooth surface before the through silicon vias.

### INTRODUCTION

Combining packaging and system on chip technologies, 3D integration is now seen as an alternative solution to the Moore's law. This technique consists in stacking functional components, interconnected by through silicon via (TSV), and thus maintaining or improving the performances of the final circuit at lower manufacturing cost than similar 2D-IC. Direct oxide bonding is a way to address high density TSV integration. Feasibility demonstrations were already achieved at the wafer level using this bonding method (1). While memory stacking is addressed by a wafer to wafer approach, the die to wafer stacking is more suitable for 3D heterogeneous integration, requesting the bonding of various dies sizes coming from different technological nodes or from different substrate material. A die to wafer stack is also the way to answer yield problems by stacking only known good dice. At CEA Leti Minatec, we are implementing an innovative die to wafer 3D integration scheme based on direct bonding and inter-die filling oxide planarisation. The main specification guide line for this new integration is to allow post processes like TSV without any impact on both the direct bonding and the inter-die oxide (meaning no new technology development to be done or any electrical performances degradation of TSV with respect to those obtained on wafer to wafer bonding).

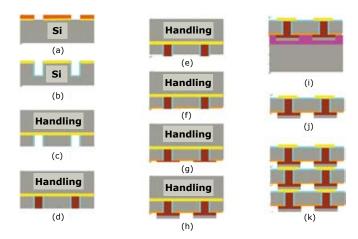

### **3D INTEGRATION SCHEME**

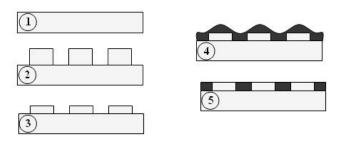

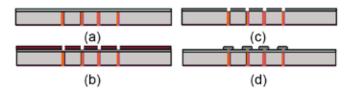

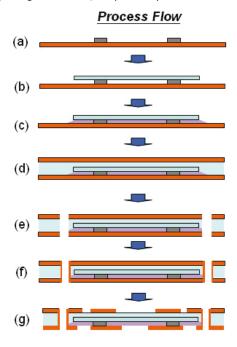

The integration scheme is the following: on a processed wafer, known good dies are bonded by face to face direct bonding in a pick and place tool either with silicon oxide layers or patterned Cu/SiO<sub>2</sub>. The dice are then thinned to the wanted thickness. A low stress high deposition rate oxide is deposited all over the structure as an inter-die filling. This oxide is thinned down to the die backside to recover a flat surface before

the whole via process is done. Each step of this scheme will be detailed in the following sections. The advantages of this technology are first that direct bonding allows the thinning of the stack down to only a few microns, then since no polymer is used for the bonding or the inter-die filling, thermal strain is reduced and reliability enhanced, finally post processes are not limited by the bonding layers stability with temperature.

Figure 1 - On a processed wafer (1), known good dies are bonded by direct bonding (2). After a first thinning of the dice (3), a low stress high deposition rate oxide is used as an inter die filling (4). A final planarization is done to allow the via post process (5).

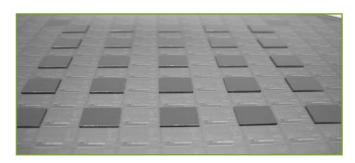

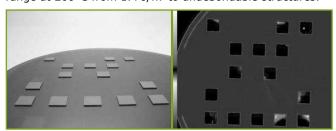

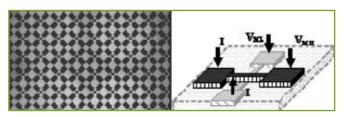

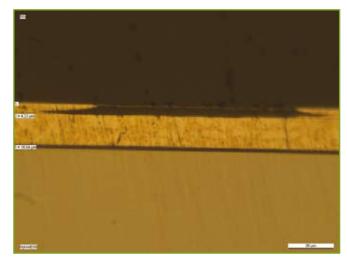

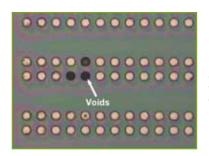

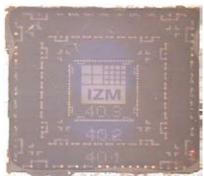

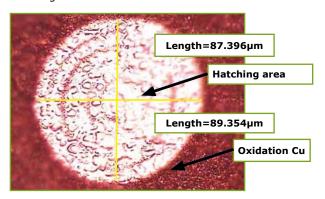

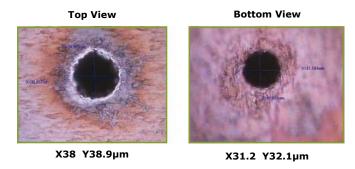

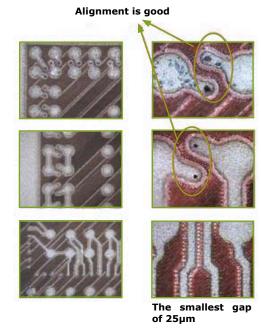

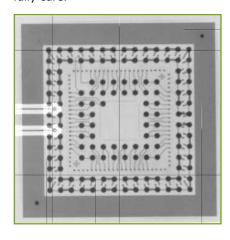

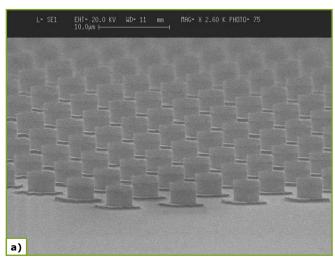

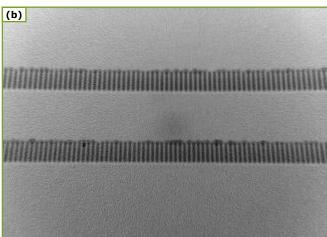

### DIE TO WAFER BONDING WITH OXIDE LAYERS

Both die and wafer present continuous surface oxide layer, with buried copper metallization for electrical tests. Surfaces are prepared for direct bonding by mean of mechanical steps (polishing) and chemical steps to achieve high hydrophilic degree. With this preparation a bonding energy G of 1.4 J/m<sup>2</sup> was measured by the double cantilever beam technique on wafer to wafer bonding. Aligned chip-to-Wafer (DtW) structures are realized in an FC300 equipment from SET to obtain the sub-micrometers alignment required for 3D high interconnection density. Pick&place is then achieved using low pressure (<500mg), at room temperature (~25°C) and for very short contact delay (<20sec). Figure 2 shows an optical microscopy observation of 25 dies bonded on a processed wafer after such a pick&place bonding and a 400°C annealing. After the 400°C annealing, a few non bonded areas are observed. Such defects are attributed to particle contamination of the wafer that occurs during the pick&place sequences. DtW alignment was controlled using Infra-Red microscopy. A misalignment below 1µm was achieved for all the structures. This indicates that high alignment quality DtW structures could be made using direct bonding and pick&place.

Figure 2 - Optical observation of 25 dies bonded on a processed wafer. The whole structures was annealing at 400°C during 2hrs.

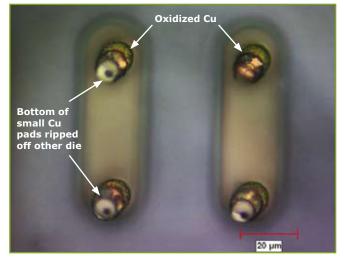

# DIE TO WAFER BONDING WITH PATTERNED COPPER/OXIDE LAYERS

Using copper at the bonding interface level is an interesting way to provide both vertical conduction and reliable mechanical toughness (2). To address 3D-ICs applications, an ambient air, atmospheric pressure, room temperature Cu/  ${\rm SiO}_2$  patterned direct bonding technology has been implemented at the die to wafer level. Low surface roughness, free contamination and flat pattern profile engineering are mandatory to enable high bonding quality (2).

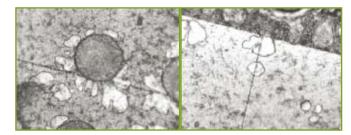

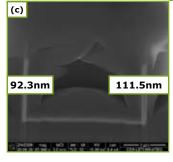

Prior to the dicing, dies are prepared by a CMP process at wafer level to monitor surface adequacy with pattern direct bonding. Since dicing induces huge particle contamination, a die cleaning process is mandatory before bonding. Die to wafer alignment and bonding are then carried out in a SET FC 150 tool. Bonding quality is characterized by Scanning Acoustic Microscopy (SAM) after 200°C/30minutes annealing step. Few non bonded areas are recorded at the patterned bonding interface induced again by particle contamination (Fig. 2). The bonding was effective with copper density of 20% (pad structure and 2% (Kelvin structure). Anyway one as to note that depending of the copper density the bonding energy will range at 200°C from 1.4 J/m² to undebondable structures.

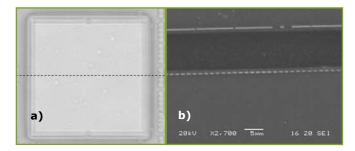

Figure 2 a et b - (left) Optical view of die to wafer SiO<sub>2</sub>/Cu patterned direct bonding, (right) Scanning Acoustic Microscopy of the same structure.

The alignment was measured on each die, thanks to cross in box, and ranges from few microns down to 0.5  $\mu$ m for the best case. The obtained alignment is limited by the capacity of the equipment with our used conditions. Die to wafer SiO<sub>2</sub>/Cu patterned direct bonding has been performed with Kelvin structures to allow fine electrical characterization of the bonding interface (Fig. 3). Kelvin structures are obtained by bonding dies on wafers having both a 10  $\mu$ m branch of the Kelvin structures. The copper to copper contact area is though  $10x10\mu$ m². The silicon substrates of the dies are removed down to oxide first mechanically and finally with a

TMAH wet etch. The silicon oxide is finally dry etched down to the bonding interface to enable probes to connect copper pads (Fig. 4).

Figure 3 - (left) Infra Red view of Kelvin test structure at the bonding interface before thinning, (right) Principle of the Kelvin structure test.

Figure 4 - Optical microscopy of the copper bonding Kelvin structure after silicon and silicon oxide etching. The pads are  $95\mu m$  large and the bonded zone is  $10x10 \mu m^2$ .

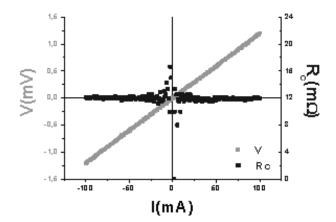

Electrical characterization was performed on 400°C/30mn annealed samples. The I(V) curve has a perfect ohmic behaviour (Fig. 5). With four point electrical characterization on Kelvin structures, one can calculate the contact resistance of the copper to copper bonding interface and its specific resistance:

$$R_{c} = \frac{V_{MH} - V_{ML}}{I}$$

$$\rho_{c} = R_{c} \times A_{c}$$

Figure 5 - V(I) and Rc(I) curve on the 10x10  $\mu m^2$  contact area of the Kelvin structure.

With  $A_c$  the copper to copper bonded area,  $V_{MH}$  the upper

layer electrical potential,  $V_{\text{ML}}$  the lower layer electrical potential and I the input current. Contact Resistance  $R_c$  is  $12m\Omega$  for  $10x10\mu m^2$  contact area and the specific contact resistance is  $1.2\Omega.\mu m^2$ .

This value is in good agreement with wafer to wafer bonding contact resistance measured on similar Kelvin structures (2). Furthermore, this resistance is negligible compare to that of TSV resistance used in 3D IC schemes (1).

### INTER DIE FILING AND PLANARISATION

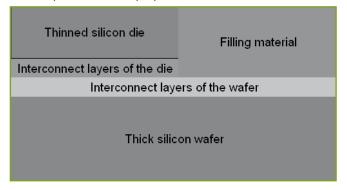

To allow the recovering of a planar surface an inter-die filling must be deposited. For industrial requirements, the filling material must be deposited with an high thickness deposition rate, not be degraded by post process steps (like a 400°C anneal for example), enable an optical alignment through the thick layer and induce a low residual stress. The chosen filling material is a high deposition rate oxide layer with residual low stress. A thickness near 30µm was deposited by PECVD (Plasma Enhanced Chemical Vapor Deposition) at 400°C. Depending on the deposition conditions, the deposition rate ranges from 1.8 to  $3\mu\text{m/mn}$  and the stress in the film as low as 15 MPa.

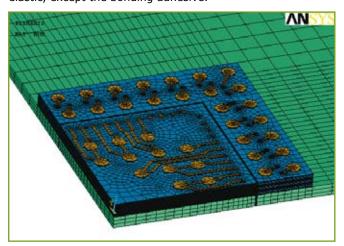

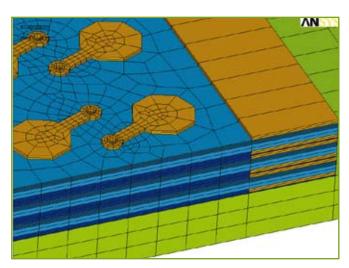

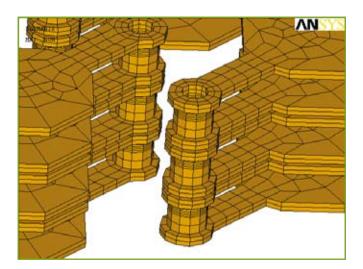

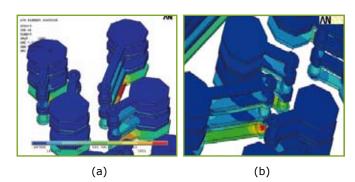

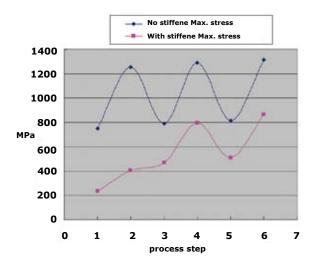

The stress induced in the dies was simulated with ANSYS software. The stack is described in figure 6, homogeneous anisotropic mechanical properties of interconnects is used.

Figure 6 - Simulated area using symmetries of the stack.

Preliminary results show a maximum stress at the edges off the silicon dies of 20 MPa, This stress does not propagate more than a few microns at the edges of the dies.

Figure 7: die to wafer structure after oxide interfiling.

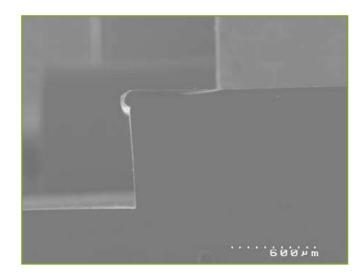

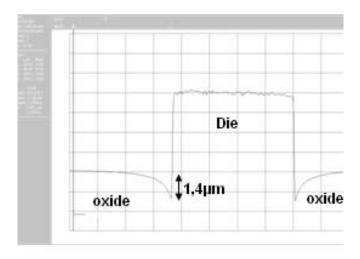

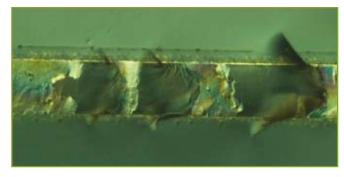

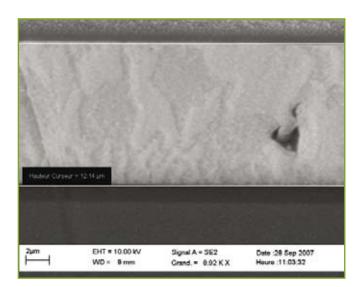

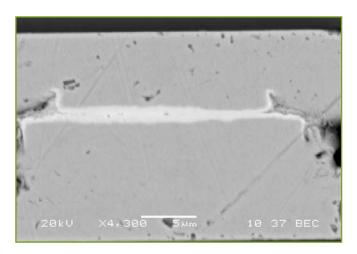

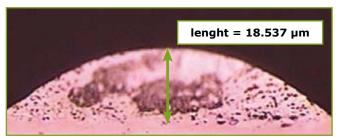

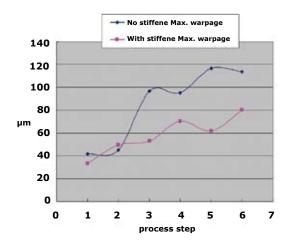

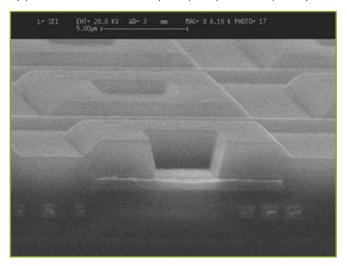

Devices won't be affected by such a stress. Figure 7 is a picture of a wafer after a 30µm thick filling oxide deposition. A recess effect at the edges of the dies appeared after the deposition (Fig. 8). This

phenomenon was attributed to a geometric effect and was easily reduced down to 1.4  $\mu$ m (Fig. 9a).

Figure 8 - MEB observation of the oxide deposition on a die, a masking effect is clearly seen at the upper corner of the die.

Figure 9a - Oxide recess after deposition measured by profilometry.

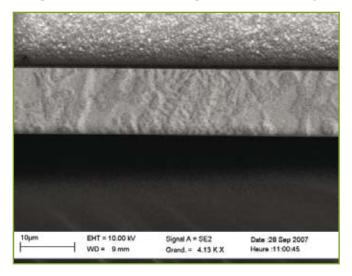

In order to recover a flat surface that would allow further technological steps involved in 3D integration processes such as lithography, TSV process or stacking of a second dies level, a planarization stage was developed.

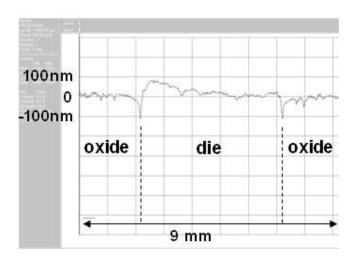

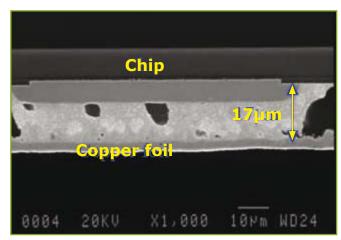

In this process, the oxide layer over the dies is thinned using grinding tools until the recess was removed. Since oxide grinding is very unusual, wheels dedicated to hard material were used. Then, a polishing step is performed to remove the remaining oxide down to the silicon backside, a non selective (Si/SiO $_2$ ) specific slurry was used in order to prevent fences creation at the edges of the dies. The targeted final thickness was 15  $\mu m$ . We obtained a "flat" mixed surface (Si/SiO $_2$ ) with a protusion of the silicon dies smaller than 150nm homogeneously on the wafer (figure 9b).

The measured surfaces roughnesses (RMS) are 4nm and 50nm for the silicon and the oxide, respectively. Improvements of this process are still under progress.

Figure 9b - mechanical profilometer scan of a mixed surface after planrization.

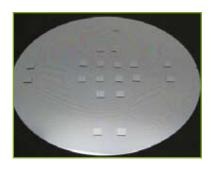

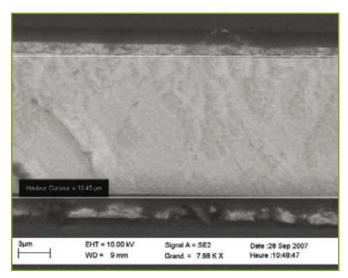

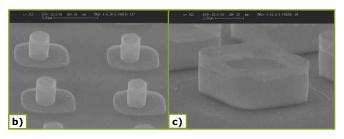

### **FINAL DEMONSTRATOR**

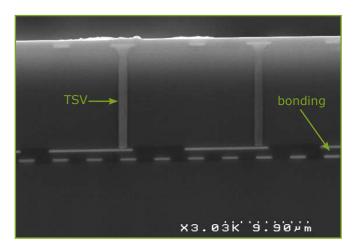

All the described steps were done on processed dies and wafers at a low temperature (< 400°C or < 200°C) to ensure the integrity of the FEOL and BEOL processes already done on the dice or the wafers (Fig. 10). A TSV process described elsewhere (1) was then applied on these wafers without any process adaptation (Fig. 11). The electrical results as for example the measured 3µm TSV resistance of 170m $\Omega$  is in good accordance with the values measured for the same structures on bonded wafer to wafer stack. Thus, the feasibility of this innovative 3D integration scheme is demonstrated,

improvements are under progress.

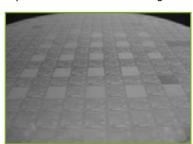

Figure 10: Optical observation of the fully planarised wafer prior to TSV process.

Figure 11 - Cross section of the final stack after the TSV process.

### CONCLUSION

Each technological step of an innovative 3D die to wafer integration scheme was developed such as: die to wafer bonding with oxide or mixed copper/oxide layer, oxide filling and planarization. and validated in an electrical demonstrator. The obtained results on the first tests are very encouraging. And this technology will be implemented.

### **REFERENCES**

- (1) P. Leduc, L. Di cioccio et al, VLSI 2008, "Enabling technologies for 3D chip stacking "proc. p.76-78 (2008).

- (2) P. Gueguen, L. Di cioccio et al. 3D "Vertical interconnects by Copper Direct Bonding", MRS fall (2008).

- (3) L. Di Cioccio et al. Enabling "3D Interconnects with Metal Direct Bonding" extended abstract IITC (2009).

- (4) P. Leduc, L. Di Cioccio et al. "Innovative 3D die to wafer integration scheme based on oxide or copper direct bonding and oxide die inter filling planarization", this conference.

## **RF MEMS and Flip-Chip for Space Flight Demonstrator**

Claude Drevon, Olivier Vendier, Antoine Renel.

Thales Alenia Space

26 av. JF. Champollion, BP1187, 31037 Toulouse Cedex 1, France,

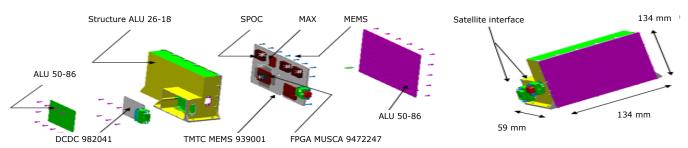

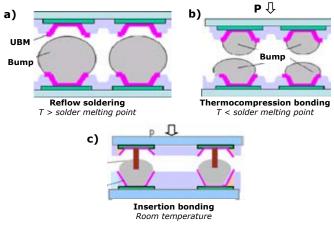

The next generation of telecommunication satellites payloads will require higher performances and higher functionality for multimedia applications with still stronger constraints on cost and size. That means higher operating frequencies (Ka band), higher flexibility, (reconfigurability, on board processing...) and further miniaturization.

In such a context, RF MEMS – Micro Electro Mechanical Systems – offer new degrees of freedom for the realization of integrated filters, tunable LC circuits, and reconfigurable antennas... They could replace solid-state components thanks to their good microwave performances and even create new functions due to their electromechanical behavior and small size.

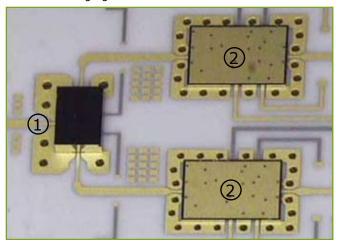

An example of an expected redundancy function is showed on the following figure.

Figure 1 - Example of future trends: self redounded Ka-Band LNA with MEMS:

(1) Flip-Chipped MEMS Switch (self-packaged),

(2) Flip-Chipped MMIC LNA.

### **RELIABILITY IN ORBIT**

For RF MEMS switches, one of the main problems to be addressed is the reliability for missions more than fifteen years and the capability to survive at the space environment. A flight demonstration could allow:

- to have the visibility of the new technology for new internal or external customers,

- to go from mid to high TRL (Technology Readiness Level) i.e. to move from «Component and/or bread-

- board validation in laboratory environment» status to «prototype demonstration in a space environment»,

- to enhance the know-how of such a technology and the associated risk assessment.

A space flight equipment has been defined to demonstrate, in flight condition, RF MEMS capability. This demonstrator has been designed to be full independent and to preserve the payload immunity.

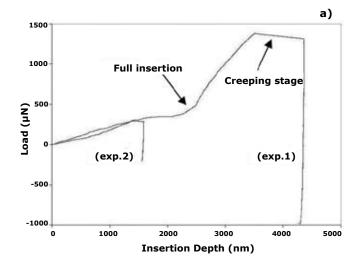

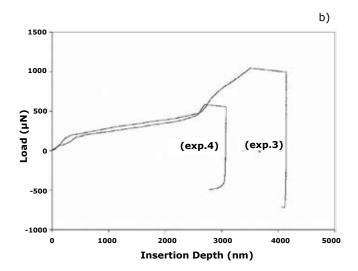

The aim of this experience is to assess the failure modes for RF switches based on ohmic contact technology, which are dealing with the stiction metal-metal at the contact level, the creep for the membrane and the dielectric charging effect due to the electrostatic activation. This will be done through DC measurements using advanced RF switch intrinsic characteristics: the contact resistance Rc during On position and the Vp (pull down voltage).

Twenty MEMS will be used for covering three functioning modes :

- 4 switches with rapid cycle 1 switching per second,

- 4 switches with medium cycle 1 switching per day,

- 4 switches with long cycle 1 switching per year,

- 4 switches will be actuated by remote control from Ground, after 10 years,

- 4 switches where pull-in voltage is monitored to estimate their eventual degradation.

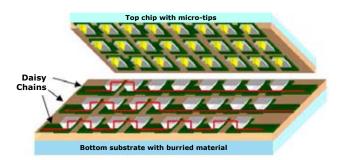

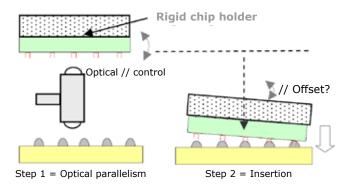

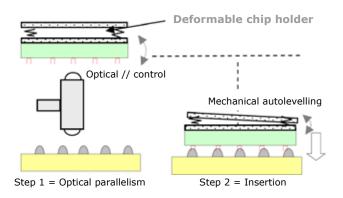

The concept of the demonstrator is illustrated on the figure 2. The RF switches are very small components that require connections as short as possible to preserve all the RF characteristics. So, flip-chip has been selected for assembling and connecting the RF switches. As the objective of this demonstrator is to measure and follow, in flight, the reliability of the RF MEMS switches, those devices will not be measured at the RF performances level. However, the use of flip-chip bonding has been confirmed to be as close as possible to the real application.

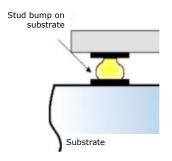

This paper focuses on the assembly of the RF switches and the associated hybrid; so, we are first going to discuss about flip-chip based on stud bumps and thermocompression assembly.

### STUD BUMPS AND FLIP-CHIP ASSEMBLY

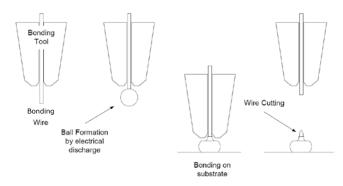

The principle of stud bumps is described on figure 3.

Figure 2 - Concept of the flight demonstrator.

Figure 3

Principle of flip-chip with stud bumps and thermocompression.

The choice of using stud bumps is driven by several reasons: shortest connections, the use of "standard" device (i.e. with only gold pads for bonding), the capability to make those bumps on any type of substrates, including in the openings of multilayer structures. From a high frequency point of view, the size of the bumps,

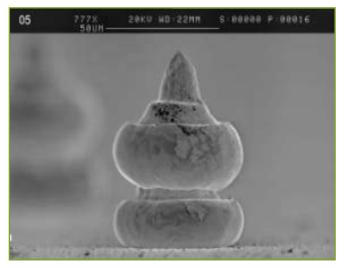

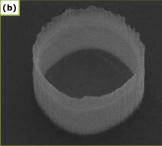

Figure 4 - Double stud bump (Ø 50  $\mu m$  - hbase = 50  $\mu m$  - htotal = 80  $\mu m$  ).

and specially the diameter, is compatible of the electrical performances. The capability to make double even triple bumps is also a key point to manage the gap between the component and the substrate. For microwave, the proximity of the substrate with the active face of a device could influence the electrical performances.

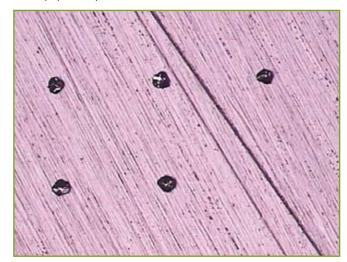

The stud bumps are made on a standard ball-bonder, with a modification of the software to allow the break of the wire at the ball level. The wire is doped with palladium to make it

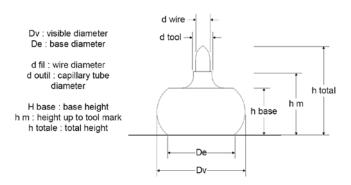

more brittle. The different steps are described on the figure 5. The size and geometry for a bump is detailed on the figure 6. One could note than the visible diameter (Dv) is smaller than the diameter (De) of the contact at the substrate level.

Figure 5 - Principle for stud bump manufacturing.

For the specification application described in this paper, we need to have higher bumps to be compliant with the thickness of the caps for the MEMS.

The sizes of those bumps and the die shear have been tested for two different lots.

For information, the minimum required by JEDEC and MIL-STD\_883D is a force of 5g/bump.

|                  | 1 <sup>st</sup> lot | 2 <sup>nd</sup> lot |

|------------------|---------------------|---------------------|

| High (µm)        | 87                  | 76                  |

| Diameter DV (μm) | 61                  | 57                  |

| Force (g)        | 21.3 g              | 26.6 g              |

A DoE (Design of Experiment) has been implemented to characterize the limits of the main parameters, which are: chip and substrate temperatures, force per bump and time of pressure. The retained criteria's are the electrical performances, the holding of the dice (including the type of break).

Figure 6 - Stud bump characterization.

Figure 7: Triple stud bump.

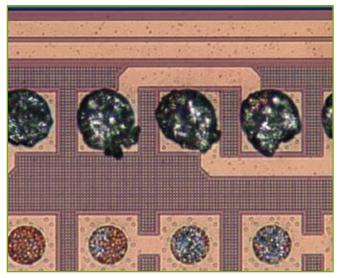

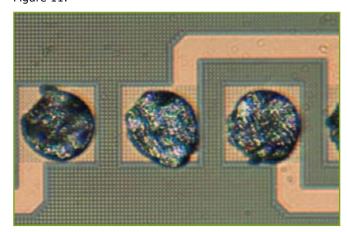

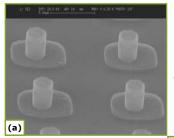

### FLIP-CHIP ASSEMBLY OF THE RF MEMS SWITCHES

20 RF-MEMS switches, from CEA-LETI, have to be assembled in hermetic packages.

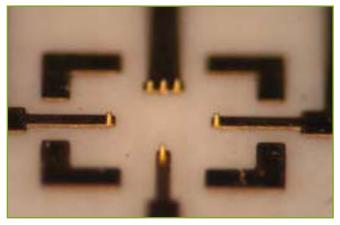

Figure 8 - Stud bumps at the substrate level.

The stud bumps are implemented on ceramic substrates (figure 8).

Figure 9 - SET FC 150 Automated Die/Flip-Chip Bonder.

Then, a **SET FC 150 Automated Die/Flip-Chip Bonder** (figure 9) is used to make the thermocompression bonding on the substrate.

Figure 10 - Bumps under the device.

The good accuracy of this bonder allowed to use very small pads and, as a consequence, to minimize the desadaptation of the RF signal in a real application. The substrate with the device is then bonded into a metallic package, which will be hermetically sealed under nitrogen.

Figure 11 - Hybrid package.

### CONCLUSION

A new equipment has been developed aiming at prove inorbit operation for new RF MEMS switches. This equipment is using an autonomous flight proven interface to the platform and is compatible of GEO telecom satellite working at 36000km.

The use of flip-chip for the connection of the RF MEMS has reduced the length of the RF/microwave connection so that all the intrinsic characteristics are presserved.

The functionality of the electrical model is validated and passed all the standard procedure applied to commercial satellite equipment (EMC, thermal vacuum, vibrations and mechanical shocks).

The fly model is produced, waiting the end of the RF MEMS qualification.  $\,$

# **Electrically Yielding Collective Hybrid Bonding for 3D Stacking of ICs**

Anne Jourdain, Philippe Soussan, Bart Swinnen and Eric Beyne.

### IMEC vzw

Kapeldreef 75, B-3001 Leuven, Belgium Tel: +32 16 281 909 Fax: +32 16 281 097 Email: jourdain@imec.be

Copyright © 2009 IEEE. Reprinted from ECTC 2009 proceedings.

14 / 80

### **ABSTRACT**

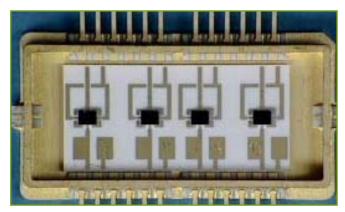

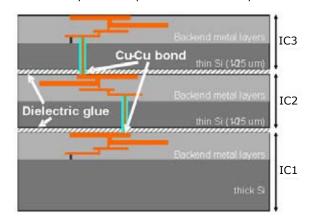

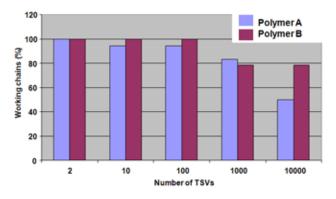

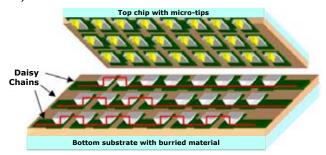

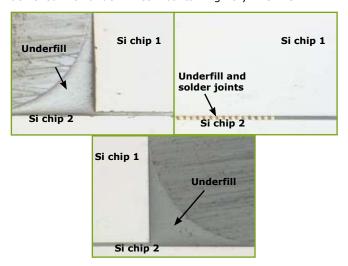

The production of non-monolithic 3D-systems by stacking and interconnecting components through substrate vias (TSVs) is intrinsically limited to the stacking of thin dies, typically ranging from 100µm down to 15µm. Since dies or wafers of such thickness are no longer rigid, it is an important requirement that the bond guarantees mechanical stability and rigidity to the thin stacked die or wafer. The route followed here combines the fixation of a thin wafer or die by means of a dielectric adhesive with the formation of a metallic interconnect. This process is called Hybrid Bonding. The introduction of a tacky polymer as an intermediate glue layer in the direct bonding scheme offers the possibility for die-to-wafer throughput optimization: the opportunity lies in the separation of die pick-and-place and bonding operations. This process is called Collective Hybrid Bonding. Two polymers have been selected (so called polymer A and polymer B) according to their reflowing and bonding properties, and a die pick and place procedure has been defined and optimized for each of them, allowing a fast and reliable operation. Moreover, electrical measurements of daisy chains showed a comparable and reproducible yield of 80% working chains up to 1000 TSVs.

### INTRODUCTION

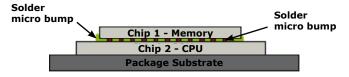

The restriction in thin die stacking not only stems from the desire to shrink system height, but is also imposed by the limited capabilities of TSV processing. Depending on the type of TSV technology employed, the final wafer or die thickness typically ranges from 100µm down to 15µm. Since dies or wafers of such thickness are no longer rigid, it is an important requirement that the bond guarantees mechanical stability and rigidity to the thin stacked die or wafer. Pure dielectric bonding guarantees such stability simply by the fact that the thin die or wafer is bonded over its entire surface. This method, however, limits the options for electrical interconnection to a via-last approach enhancing the risk of system yield loss during via processing. A very recent approach combines fixation of a thin wafer or die by means of a dielectric adhesive with the formation of a metallic interconnect. This is typically the route followed by IMEC and is so called 3D-Stacked IC (3D-SIC) [1,2]. An illustration of this 3D concept is shown in Fig.1. In this approach, standard single damascene techniques are combined with extreme wafer thinning and direct Cu-Cu thermo-compression bonding.

In this integration scheme, a die-to-wafer stacking approach is preferred: indeed, as compared to wafer-to-wafer

bonding, it may be of more interest for the fabrication of heterogeneously integrated systems as it does not impose the requirement of equal die size. The method is also compatible with the selection of Known Good Die prior to stacking and, therefore, is of interest in cases where one of the components in the stacked system is a product with limited yield.

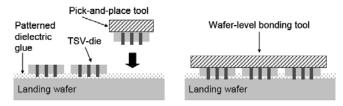

Figure 1 - Illustration of the 3D-SIC concept: dies are separated by a thin dielectric glue layer, and interconnected through Si Cu vias (TSVs).

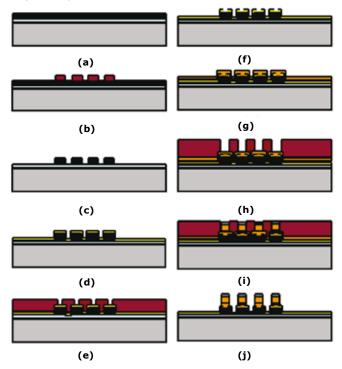

The cost of die-to-die or die-to-wafer stacking for most bonding methods is limited by the throughput of the process, especially when heat needs to be applied to achieve the bond, which is a lengthy process. The introduction of a tacky polymer as an intermediate glue layer in the direct bonding scheme now offers the possibility for die-to-wafer throughput optimization. This process is called **Hybrid Bonding**. The opportunity lies in the separation of die pick-and-place and bonding operations. First, the TSV-dies are aligned and placed onto a landing wafer on which the polymer glue layer has been previously processed and patterned (by standard photolithography step). This patterned and tacky dielectric weakly bonds the stacked dies and fixes them during further handling. This operation is performed ideally at low temperature with the pick-and-place process repeated until the full wafer is populated. In a second stage, the fully populated wafer is moved to a wafer-level bonding tool where pressure and heat are applied to all stacked dies at once.

Thus, the dielectric layer reflows and the metallic interconnect bonding is performed for all stacked dies simultaneously. This process is called **Collective Hybrid Bonding** and is illustrated in Fig. 2.

Figure 2 - Illustration of the die pick and place and the collective hybrid bonding process.

The choice of the intermediate glue layer depends not only on its bonding properties that have to be compatible with the Cu-Cu direct bonding process, but also depends on its capability of reflowing and deforming upon application of pressure during the collective bonding process to allow good electrical interconnections between the different top dies and the landing wafer. Two polymers have been selected (so called as **polymer A** and **polymer B**) according to these criteria, and a die pick and place procedure has been defined and optimized for each of them.

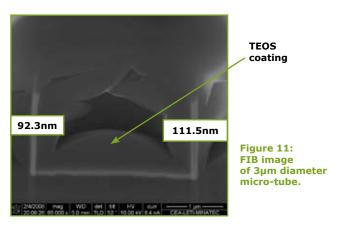

### DIE PICK AND PLACE AND HYBRID COLLECTIVE BONDING

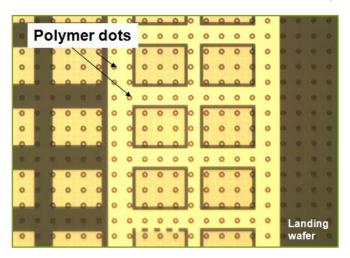

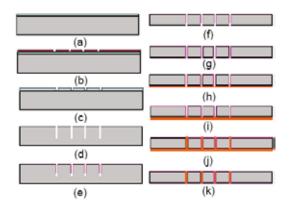

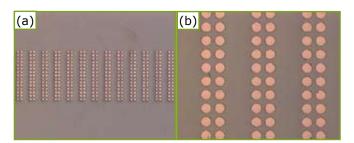

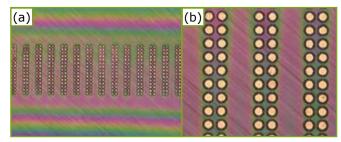

Different landing wafers were processed by standard photolithography with respectively polymer A and polymer B as glue material. Patterning of the polymer glue layer is required as the collective bonding relies on the reflow and the deformation of the material upon application of temperature and pressure. The patterning of the polymer glue layer results in a uniform distribution of tiny dots across the wafer surface as shown in Fig. 3, except in locations where TSVs will make an electrical contact after bonding.

Figure 3 - Optical picture of a landing wafer after dielectric patterning showing a uniform distribution of polymer structures (dots).

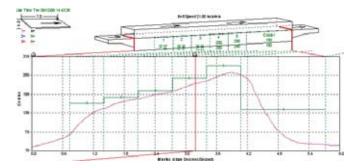

The lithography process has been optimized for both polymers to result in a layer thickness slightly higher than the initial TSV hight (typically  $0.7\mu m$ ). The idea of the pick and place procedure is to connect at low temperature the top die to the landing polymer glue layer only, in a fast and reliable operation, leading to a high throughput process. The experimental pick and place operation has been performed at die level (after dicing of the landing wafer) on a flip-chip bonder

type **FC150**. Different die attach conditions in pressure, time and temperature have been evaluated.

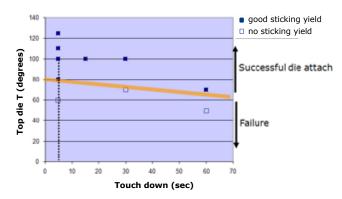

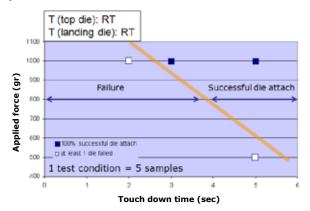

Figures 4 and 5 show the test conditions as used to determined reliable pick and place conditions both for polymer A and polymer B. Each condition has been tested on 5 samples. The success criteria is defined as 'all 5 samples stay in place'. The experiments clearly show the existence of 2 regions: the first region systematically leads to failure (at least 1 die fell off), and the second determines a safe set of conditions for which a reliable die attach is obtained.

Figure 4 - Die pick and place experimental conditions as function of top die temperature and contact time as used for polymer A.

Figure 5 - Die pick and place experimental conditions as function of force and contact time as used for polymer B. Note that both top and bottom dies stay at room temperature.

As shown in Fig. 4 for polymer A, a reliable die attach occurs for top die temperatures above 80°C while the landing die including the polymer layer stays at room temperature. It is an important parameter to keep the bottom die at low temperature to prevent polymer curing during the pick and place operation that would lead to failure. The best conditions have been established for a top die temperature of 100°C, a bottom die at room temperature, a touch down (or contact) time of 5 sec and 10kg force. Lowering the force or further decreasing the touch down time lead to systematic failure (all dies fell off). Concerning polymer B (Fig. 5), both top and bottom dies stayed at room temperature. The variables here are touch down time and contact force. As previously mentioned, the definition of a successful die attach region allows to determine reliable and repeatable bond conditions. As compared to polymer A, a much lower force has to be applied for much shorter times. The best conditions have been

established for a room temperature process, 1kg force and 3sec contact time. With this respect, polymer B is a better candidate than polymer A. A significant reduction in bonding force and contact time makes polymer B an attractive material for die pick and place.

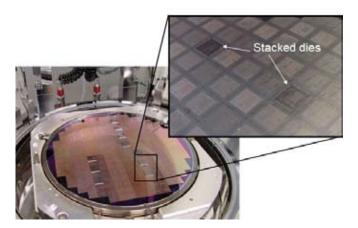

Figure 6 - Picture of a landing wafer after pick and place of 10 TSV dies and collective hybrid bonding.

The next step in 3D stacking is the collective hybrid bonding operation. After populating a landing wafer (including the patterned polymer layer, A or B) with TSV dies and using the best known method as described previously, the landing wafer is transferred in a wafer bonder.

The final bonding process is performed in 2 steps: in the first step at relatively low temperature, the polymer reflows and deforms upon application of a force, putting into contact the Cu TSVs of the top die and the Cu landing pads. In the second step, the temperature is further increased to realize the Cu-Cu direct bonding, and at in the same time the electrical connections between top and bottom Cu layers. A picture of a landing wafer after collective hybrid bonding is shown in Fig. 6. Electrical measurements of daisy chains showed a comparable and reproducible yield of 80% working chains up to 1000 TSVs, both for polymer A and polymer B, as shown in Fig. 7.

Figure 7 - Electrical yield obtained on 10000TSV daisy chains after collective hybrid bonding with respectively polymer A and polymer B.

### CONCLUSION

The 3D stacking approach proposed here relies on the introduction of a tacky polymer as an intermediate glue layer in the direct bonding scheme. It offers the possibility for dieto-wafer throughput optimization. The opportunity lies in the separation of die pick-and-place and bonding operations. Two polymers have been selected according to their reflowing and bonding properties, and a die pick and place procedure has been defined and optimized for each of them. The best known method allows a die pick and place at room temperature, with an indicative throughput of a few seconds per die placement (excluding alignment). After collective hybrid bonding of TSV dies to a landing wafer, electrical measurements of daisy chains showed a comparable and reproducible yield of 80% working chains up to 1000 TSVs.

### **REFERENCES**

- [1] A. Jourdain, S. Stoukatch, P. De Moor, W. Ruythooren, S. Pargfrieder, B. Swinnen and E. Beyne,, "Simultaneous Cu-Cu and Compliant Dielectric Bonding for 3D Stacking of ICs", Proc. IITC Conference, June 4-6, 2007, Burlingame, CA, pp. 207-209.

- [2] B. Swinnen, A. Jourdain, P. De Moor, E. Beyne C. in "Wafer Level 3-D ICs Process Technology"; edited by S. Tan, R.J. Gutmann, and L.R. Reif (Eds), Springer, ISBN 978-0-387-76532-7, 2008.

# A Fluxless Bonding Process using AuSn or Indium for a Miniaturized Hermetic Package

Marion Volpert<sup>1</sup>, Christophe Kopp<sup>1</sup>, Julien Routin<sup>1</sup>, Adrien Gasse<sup>1</sup>, Stéphane Bernabe<sup>1</sup>, Cyrille Rossat<sup>2</sup>, Myriam Tournair<sup>2</sup>, Régis Hamelin<sup>2</sup>, Vincent Lecocq<sup>2</sup>.

¹) CEA, LETI, MINATEC: 17 rue des Martyrs, F-38054, Grenoble, France - marion.volpert@cea.fr - +33 4 38 78 24 33

) INTEXYS PHOTONICS:

Copyright © 2009 IEEE. Reprinted from ECTC 2009 proceedings.

### **ABSTRACT**

In the field of high speed data transmissions or in the industrialisation of MEMS devices a hermetic package is often required. However this technological achievement represents an important part of the package price and usually limits the freedom of design and miniaturization. In this paper we propose a localized hermetic sealing method adapted to batch process, that uses either Eutectic AuSn (AuSn20) or pure Indium for the seal ring. A novel fluxless controlled thermocompression process is developed to achieve simultaneously a hermetic bonding and interconnection of I/Os located within the sealing ring through the capping part. Different designs are tested using a standard He aspersion leak test and additionally some reliability tests are performed. Leak rate <5.10-8 mbar I/s are obtained with both AuSn20 and In seal rings.

### INTRODUCTION

For a long time optoelectronic modules have been dedicated to high added value applications like fiber optic telecommunications. The standard packaging solutions still used in this field are based on multi part optical assemblies hermetically sealed in high cost housings like butterfly packages [1]. More recently, optical links have spread in local loop networks, like Ethernet LANs, Fiber Channel SANs, and Internet switches. These newer applications require high speed high density optical channels at lower cost per data rate. Standard hermetic sealing processes using metallic leads, typically Kovar (Fe-Co-Ni) and local glass solder seals, are very prohibitive and not adapted to these low cost applications. The sealing methods imply either very high temperatures that are above 400°C for glass solder, or resistance welding which is expensive and is limited to a unit process. A batch process which achieves miniaturization of the package is necessary. In the market of MEMS, accelerometers, which are the main industrialized MEMS product used in airbags are typically sealed using a glass frit bonding technology (Bosch). However, as the market tends to go towards miniaturization, metal will prove to be the best choice for hermetic purpose. When reduced to extremely thin wall thickness (10µm) the permeability of metal over glass will hold for much longer (100 years compared to a year). With RF-MEMS device packages, the use of eutectic gold-tin is being investigated [2]. In the optoelectronic package there are today some developments for cheaper and smaller encapsulation using metal seal rings, typically made of AuSn preforms [3]. However the use of AuSn preformed rings has some drawbacks, it is deposited unitarily over the lid or the base and the width of the ring may not be reduced below 400µm for fabrication and handling purposes. Therefore these solutions remain costly and do not properly address the demand for reduced footprint and cost reduction in today's packages.

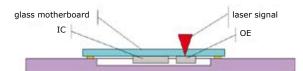

At LETI, we also have developed a 4-channel high data rate (10 Gbps) small-form factor transceiver [4], shown figure 1. The design of this module is based on an advanced Multi Chip Module technology and embeds optoelectronic devices (laser diode and photodiode arrays) as well as the control electronic ICs (multichannel driver and transimpedance amplifiers respectively).

Figure 1 - Schematic of a 4-channel high data rate transceiver.

In order to keep a high degree of reliability required for the application, an original packaging strategy has been developed. The glass motherboard is assembled onto a ceramic package, for example a 44 pad Leadless Chip Carrier with standard dimensions (17x17mm<sup>2</sup>) made of alumina. The use of a LTCC cofired ceramic package also permits to dramatically reduce cost compared to metallic packages when high quantities are addressed.

On the upper surface of the ceramic package, metalized rings and pads have been designed with the same pattern as on the glass motherboard. The pads are connected to metallic vias that interconnect the electric signal to the pads located on the lower side of the ceramic package. As a result, it is possible to hermetically assemble the glass motherboard onto the ceramic package using solder rings and connecting pads. Hermeticity and electrical connections are simultaneously obtained during the sealing process. Some prototypes were first achieved using non hermetic seals and hermetic seals using AuSn20 preforms.

The development of such packages requires advanced sealing technologies, intended to reduce cost. The remaining of this paper describes the current work on sealing technology for miniaturization.

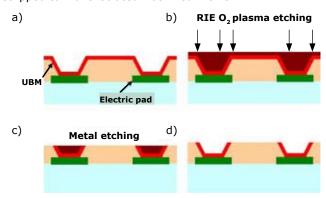

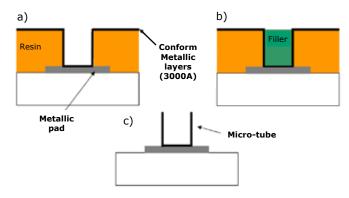

### **FABRICATION PROCESS AND SAMPLES DESIGN**

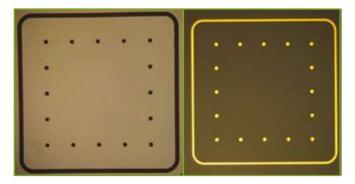

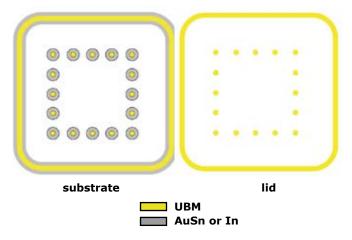

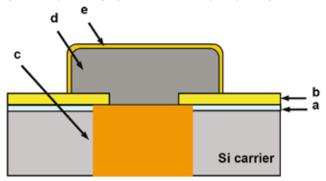

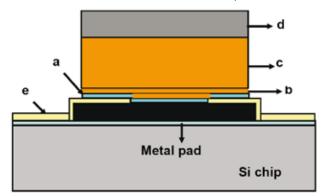

To further study such hermetic seals, work on a batch process, optimize the design and solder materials, some test samples are achieved by designing seal rings and connecting pads using sputtering deposition of AuSn20 or evaporation deposition of Indium solder on silicon substrates. Quartz or pyrex chips are used to model the hermetic lid. To achieve the hermetic seal we use AuSn20 and In as the solder material. AuSn20 is already used for fluxless assembly needed in hermetic bonding and leads to stable bonds over time with very high shear strengths. However, its relatively high melting temperature and hardness limits its application where the thermomechanical stress remains low. For this purpose Indium, which has a much lower bonding temperature and which is adapted for the assembly of parts with a CTE mismatch, is also studied. In both cases an evaporation deposition and lift-off process are used to implement and pattern the solder. This technique, in addition of being a batch process, achieves a solder ring with a width well below 100µm, which greatly reduces the footprint of the package. The samples are prepared with ring dimensions of 6mm x 6mm and ring width of 60µm to 105µm for the assembly of quartz on silicon which has a CTE mismatch between 3 and 4 and pyrex on silicon which have matched CTE. With these samples the influence of the thermomechanical stress will be tested over the different solders. Additionally, some connecting pads are implemented within the seal ring to reproduce the I/Os. After deposition the solders are reflown to form smooth ring, ready to be assembled.

Figure 2 - Test samples: Seals rings and output pads on the silicon substrate and lid.

Different processes are tested for the reflow and lid assembly. Visual observations, cross sections and shear tests are performed to estimate the quality of the bond.

Finally, leak tests before and after thermal shocks are performed to obtain a final qualification of the samples and determines the optimum assembly parameters.

The AuSn20 test samples, shown Figure 2, are fabricated by Reinhartd Microtech in Switzerland [5]. The deposition is achieved by alternately sputtering thin layers of gold and tin under vacuum with a total deposition thickness of 4.5 µm. 100 mm silicon wafers are used to fabricate the substrate and pyrex wafers as well as quartz wafers are used for the lids. The solders are only deposited on the silicon substrates and an Under Bump Metallization (UBM) which consists on an adhesion and diffusion layer as well as a solderable layer is deposited on the pyrex and quartz lids. The top layer is Au which is a good wetting layer, with 0.1 µm to

0.2µm thickness not to modify the gold tin ratio after reflow.

The In test samples are fabricated at CEA using the same mask as the AuSn20 samples. 4.5µm of In is deposited using a chemical vapor deposition followed by a lift of process. The same lids are used for the assembly.

### **SAMPLES DESIGN**

The rings are 6mm square with varying widths from  $60\mu m$  to  $105\mu m$  and the interconnect pad diameters vary as well from  $60\mu m$  to  $105\mu m$ . The substrates and lids have matching design so that the ring and output pads correspond to each other, however, the width of the ring may vary between the two. A schematic of the solder and under layer is shown in figure 3.

Figure 3 - Rings and bumps designed.

It has been previously observed that the design of the deposition ring and its under layer require special care otherwise there is a risk of local excess of metal upon reflow. Different combinations between the width of the ring, the under metal layer on the substrate and on the lid are therefore tested. These differences achieve different ring height and bump height, the bumps being slightly higher than the ring after reflow. The ring squares have rounded corners and some geometric changes within the under metal layer are also tested to reduce the possibility of metal excess after reflow. A total of 64 configurations are tested.

### **REFLOW PROCESS**

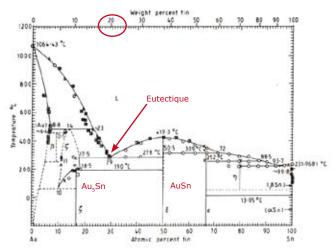

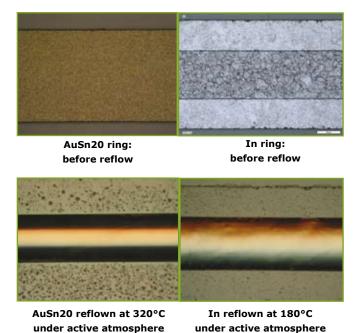

The reflow process is necessary in both cases to obtain the desired geometry before assembly. Upon reflow, smooth rings and bumps with the proper height are obtained and in the case of AuSn20 the eutectic gold tin which consists of a mixture of the  ${\rm Au}_5{\rm Sn}$  phase and AuSn phase (see figure 4) is generated. For this step a liquid flux or an active atmosphere is possible since it may be followed by a cleaning step. Indium is well known in the field of infrared detector [6] and its reflow process straightforward under flux or active atmosphere.

The reflow process is generally performed for a few minutes at about  $15^{\circ}\text{C}$  higher than the  $156^{\circ}\text{C}$  melting temperature

of In. AuSn20 is generally deposited by electroplating [7], or molded into a preform, but on rare occasions deposited by sputtering as described above.

In all cases a reflow process is necessary. For preform it achieves the mechanical contact between the under layer and the preform and a tacking medium is often used after the placement of the preform. In the other cases the formation of the eutectic phase needs to be achieved. It can be seen from the phase diagram that a slight increase of Sn or Au in the solder changes dramatically the reflow temperature. In addition, if the phases are not carefully controlled the mechanical properties and the intermetallic compounds are modified [8]. So the ratio between Au, Sn and the Au under layer must be carefully chosen and controlled upon deposition. Different techniques are possible to create the eutectic. One process consists of aging the samples in a reflow oven under vacuum for 4h at 200°C [9].

Figure 4: AuSn Phase diagram.

However, it is faster to use a reflow process between 310°C to 320°C under an active atmosphere [9,10] for just a few minutes.

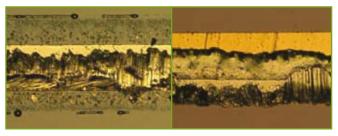

This step is a critical part of the whole assembly process so the AuSn20 behavior is first studied before working with the designed samples. We use some AuSn20 preform on silicon substrate to first qualify the behavior of eutectic gold tin with respect to varying temperature, atmosphere (active or non-active) and observe its wettability as well as its mechanical behavior. The reflow temperature is varied from 300°C to 400°C and the time at peak temperature is varied from 30 secto 10min.

The results are shown in figure 5:

320°C under N<sub>2</sub>H<sub>2</sub> or N<sub>2</sub>

400°C under N<sub>2</sub>H<sub>2</sub> or N<sub>2</sub>

300°C under active atmosphere

Figure 5 - Behavior of AuSn perform upon reflow.

All the preforms are the same size. Since AuSn20 does not wet silicon, the preform should reduce its contact with silicon and form a nice sphere after reflow. All the preforms start melting at 280°C, but only with an active atmosphere does the solder form a nice sphere. Under non-active atmosphere the preform does not de-wet the silicon substrate and the surface tension forces are not strong enough to break an oxide layer that has formed. The temperature has a limited effect compared to the atmosphere activation.

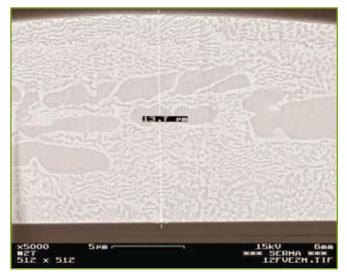

Figure 6 - SEM Image of a reflown sample showing the formation of the Au-Sn eutectic phase.

From these experiments a reflow process with an active atmosphere under 320°C is chosen for our samples. After reflow, not only must the geometry and final surface be perfect to achieve hermetic sealing with the lid, but also the metallurgy of AuSn20 must be carefully controlled. It is therefore necessary to verify that the proper intermetallics are achieved. Some SEM images of cross samples, showing the metallurgy of AuSn20 are seen figure 6. The dark phases represent AuSn and the light phase  $\mathrm{Au}_{\mathrm{S}}\mathrm{Sn}$ . It can be seen that the solder exhibits a nice mixture of both phases with slight local excess of AuSn. Optical observation of the rings can also

be seen in figure 7:

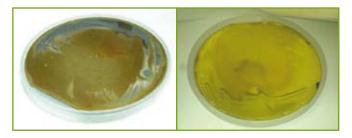

Figure 7 - Reflown samples.

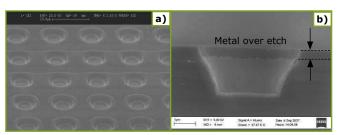

Figure 7 shows the results for both AuSn20 and In rings. The  $4.5\mu m$  layer deposited changes into a nice smooth  $10\mu m$  to  $20\mu m$  high ring. Both processes work very well for this operation however the different design leads to different results. Indeed if the ratio between solder material and under bump layers is not carefully chosen some material excess is locally observed, especially on the ring corner as shown figure 8.

Figure 8 - Local material excess upon reflow.

Finally, this step, which is critical for the rest of the process, is controlled by two major aspects. First, the solder material must be carefully controlled to obtain a good reflow and second, the design must be carefully studied to prevent local defects. If it is rather simple to reflow a sphere, it becomes very challenging to control the solder geometry over an entire ring. Only 14 configurations are finally kept, which lead to ring height from 10 to 20µm. AuSn20 and In lead to the same results so that the same configurations

are kept for both solders. This step proves, however, to be easier with In as no eutectic formation is necessary. The mechanical properties and reflow temperature are dependant of the metallurgy and to obtain a good eutectic solder an homogenous mixture of  $\mathrm{Au_s}\mathrm{Sn}$  and AuSn must be achieved. Additionally the sphere height is designed to be slightly higher than the ring's so that the bumps first contact the lid and helps the auto-alignment of the lid over the substrate. Upon assembly the bumps spread over the lid UBM and the ring contacts the lid (see figure 9, patent US6566170B1 1).

Figure 9 - Bumps and ring height before and after assembly.

### **ASSEMBLY PROCESS WITH EUTECTIC GOLD TIN**

This process must be performed in a clean atmosphere,  $\rm N_2$  or under vacuum as after sealing the cavity within the ring remains hermetic. Some gas could damage the active components within the cavity and reduce the lifetime.

Different parameters are studied to optimize these assemblies: the sample preparation, the temperature and the assembly time, and finally the pressure applied. For this process step we use a flip-chip equipment, **FC150**, developed at SET [11]. This type of equipment enables to adjust the important parameters and to achieve batch processing [12].

As stated earlier two different lids are tested: quartz, which has a CTE of about 0.5 ppm or pyrex, which has a CTE matched with silicon. The quality of the assembly is determined by the wettability of the solder, the height of the final ring, the shear strength and finally the leak rate.

Figure 10 - Assembly of Si and quartz samples exhibiting cracks.

The first samples are assembled under  $N_2$  without any prior preparation at 320°C for a few minutes. However some optical observations after bonding and after lid removal show several problems. First, with the quartz sample, the CTE mis-

match between Si and quartz is too high and causes local cracks on the lid at this temperature (figure 10). AuSn20 is a very hard solder and does not deform under stress so that the difference in deflection causes the quartz to break.

Second, if the pyrex samples are properly assembled some wettability issues are observed after removal of the lid (Figure 11).

Figure 11 - Optical observation of the lid after removal.

Optical observations of the lid after removal show some zones where the ring does not wet the UBM. This problem is only observed on the ring as all the bumps properly wet the lid. Again, some of the challenges arise from the complex geometry of the sample.

It is then decided to test only the pyrex lids, which have a CTE matched with silicon, and to improve the process by preparing the surface before assembly. Two different preparations are tested, a deoxidization of the solder with an acid prior to assembly and a cleaning of the surface with an oxygen plasma. More assemblies are performed at 330°C under a confined Nitrogen atmosphere.

Additionally another process, called reflow compression, using pressure is tested. Because AuSn20 is a very hard material the samples are also heated and some mechanical stoppers are used to prevent full collapse of the solder.

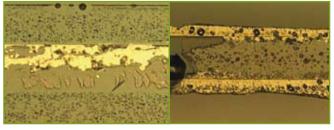

The results show very good bonding in all cases. Cross sections are observed with an SEM and the shear force of the joint is also measured using a Condor shear tester from Xyztec. The values vary from 54MPa to 113MPa, the lower forces are found for the samples assembled under Nitrogen and the higher forces for those assembled by reflow compression.

However, a sample that is subjected to an oxygen plasma prior to assembly has the highest value, proving that with a very clean surface the bonding strength is enhanced. It is also interesting to note that the shear failure occurs within the UBM for all substrates except those that are exposed to an oxygen plasma prior to assembly, confirming the idea that the cleaner surface facilitates the liaisons between the solder and the under layer (Figure 12).

Substrate with plasma O<sub>2</sub> prior assembly after shear test

Corresponding assembled chip after shear test

Substrate assembled under reflow-compression after shear test

Corresponding assembled chip after shear test

Figure 12 - Samples after sheatest.

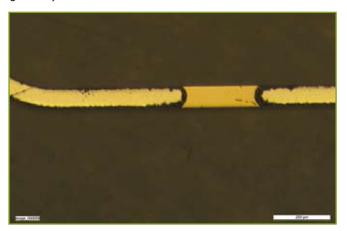

The cross sections presented in figures 13 through 16 show two phenomena. First, some voids are observed within the ring after assembly, mostly with the reflow process. Second, some delamination is observed between AuSn20 and the UBM of the lid.

Following these observations a series of 15 samples are assembled, 9 using the reflow process with either acid or plasma pre-treatment and 6 using the reflow compression process with acid pretreatment. For these samples the ring width varies between  $60\mu m$  to  $105\mu m$  so that after reflow the ring height varies between  $10\mu m$  to  $20\mu m$ .

Figure 13 - Delamination observed after reflow assembly between AuSn20 and the UBM.

Figure 14 - Voids within the ring after reflow assembly.

Figure 15 - Zone without defects after reflow assembly.

Figure 16 - Assembly with reflow compression process.

### **HERMETIC TESTS**

Hermetic tests are performed on these samples to evaluate the quality of the final bond. The hermetic measurements are performed following the MIL-STD-883 $^{\rm E}$  norm. Two different tests must be performed, a fine leak test which should measure the leak rate down to about  $1.10^{-9}$  mbar I/s depending on the equipment sensitivity and a gross leak test which should measure the leak rate down to  $1.10^{-2}$  mbar I/s. The gross leak rate is done using a perfluorocarbon liquid (Galden O2 from ISATIS) which is heated to  $125^{\circ}\mathrm{C}$ , the condition of the testing does not exactly follow the norm since the indicator fluid used is air, and the device is not placed in a vacuum/pressure chamber prior to testing.

However, this test is fast and simple and manages to eliminate quickly the samples with major defects. For fine leak test we follow the A4 test condition procedure. In this method a fixture is directly mounted onto the leak detector (a He spectrometer) and proof of the fixture integrity is first performed (that is no leak at the interface between the fixture and the detector). A cavity is drilled with a micro drill through the package to be tested then, it is mounted hermetically to the fixture. The external portion of the package is flooded with Helium gas and the measured leak rate must not exceed  $5.10^{-8}$ . The sensitivity of our device here is  $1.10^{-10}$  so that using an aspersion method both fine leak and gross leak should be detected.

| N° | Process                                        | Leak rate<br>(mbar l/s) |

|----|------------------------------------------------|-------------------------|

| 1  | Acid treatment + 330°C N <sub>2</sub> reflow   | 1.10-9                  |

| 2  | Acid treatment + 330°C N <sub>2</sub> reflow   | 1.10-2                  |

| 3  | Acid treatment + 330°C N <sub>2</sub> reflow   | 2.8.10-3                |

| 4  | Acid treatment + 330°C N <sub>2</sub> reflow   | 2.10-3                  |

| 5  | Acid treatment + 330°C N <sub>2</sub> reflow   | 2.10-2                  |

| 6  | Acid treatment + 330°C N <sub>2</sub> reflow   | 2.5.10-2                |

| 7  | Plasma treatment + 330°C N <sub>2</sub> reflow | 2.10-4                  |

| 8  | Plasma treatment + 330°C N <sub>2</sub> reflow | 1.2.10-5                |

| 9  | Plasma treatment + 330°C N <sub>2</sub> reflow | 2.10-8                  |

| 10 | Plasma treat. + 330°C reflow compression       | 1.10-9                  |

| 11 | Plasma treat. + 330°C reflow compression       | 1.10-2                  |

| 12 | Plasma treat. + 330°C reflow compression       | 1.10-8                  |

| 13 | Plasma treat. + 330°C reflow compression       | 7.10-10                 |

| 14 | Plasma treat. + 330°C reflow compression       | 5.4.10 <sup>-9</sup>    |

| 15 | Plasma treat. + 330°C reflow compression       | 2.10-4                  |

Table 1 - Leak rate measured for all samples.

With a pressurized chamber test method the time between

immersion in He and detection is generally too long to detect gross leaks as the gas has already left the sample before being measured, however, in the aspersion method the immersion in He and the detection are achieved at the same time. The results are summarized table 1.

The acceptable limit is set to 5.10-8 mbar I/s according to norm 1014 of the MIL-STD-883<sup>E</sup>, which is achieved for 2 samples with  $\mathrm{N}_{\scriptscriptstyle{2}}$  reflow and 4 samples with reflow compression. The pretreatment seems to help and a combination of the two may lead to better results. Only 2 samples out of 9, have a leak rate below the limit for the reflow process. It is therefore possible to use this method for hermetic bonding but some improvements are necessary to increase the yield. The problems probably arise from holes within the AuSn20 ring which is a common effect with gold tin when no pressure is applied. A vacuum environment would probably be very useful in this case. With the reflow compression method, 4 samples out of 6 are within SPEC, which is a very good result. In addition the height of the ring after assembly is controlled. It is suspected that with both methods, some issues arise from defects within the ring after reflow. In both cases, the ring width does not have a significant effect and no differences are observed in the result. In the case of the reflow process the final height of the assembly is a few microns shorter than after reflow and in the case of reflow-compression process the final height is defined by the stopper height. The stopper height is generally chosen a few microns shorter than the ring height. However, no optimization of the stopper height and thus seal height is achieved in this study.

### **ASSEMBLY PROCESS WITH IN**

Indium is not usually used for hermetic assembly, however, it is a soft solder that reflows at low temperature (156°C) and therefore presents two advantages over AuSn20 to accommodate the CTE mismatch. In the field of infrared, it is often used with flux as it usually exhibits a thick oxidation layer which must be reduced before assembly. In this study the use of flux is prohibited so a thermocompression assembly method is investigated. As stated above, the same samples as with gold tin are used.

A preliminary study using temperature from  $100^{\circ}\text{C}$  to  $150^{\circ}\text{C}$  and pressure from 10 to 50MPa with different sample preparations is first performed. The samples are finally assembled at  $125^{\circ}\text{C}$  under 40MPa, right after a reflow process which helps limiting the oxidation layer. The assembly time is varied from 1, 3 and 5 min, some stoppers are also added to control the final ring height. After inspection, these samples are tested with the gross leak test in order to qualify the different assembly times. The results show respectively a 15%, 50% and 100% hermetic yield for 1mn, 3mn and 5mn, proving the major impact of the assembly time. It can be explained by looking at the interdiffusion equation between gold and 1n [13]:

### $V (\mu m/h) = \exp(-8410/T) + 20,35 (T en Kelvin)$

So that at 125°C the  ${\rm AuIn_2}$  intermetallic layer that forms between gold and indium thickens over time and can be compared with that of a reflow assembly at 180°C under flux (Table 2).

| T<br>(°C) | V<br>(µm/h) | Time<br>(s) | AuIn <sub>2</sub><br>thicknesses (nm) |

|-----------|-------------|-------------|---------------------------------------|

| 125       | 0,46        | 60          | 8                                     |

| 125       | 0,46        | 180         | 23                                    |

| 125       | 0,46        | 300         | 38                                    |

| 180       | 5,96        | 20          | 33                                    |

Table 2 - AuIn<sub>2</sub> intermetallic layers thicknesses calculated with different assembly parameters.

From this table it is clear that to obtain similar intermetallic layers between a reflow or a thermocompression assembly it is necessary to keep the pressure and the temperature for at least 5 min.

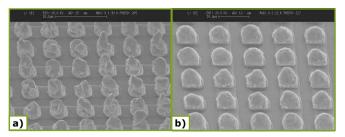

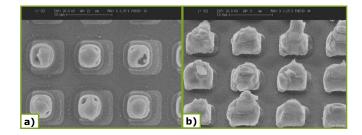

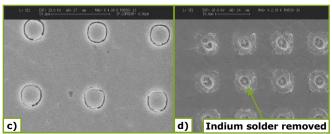

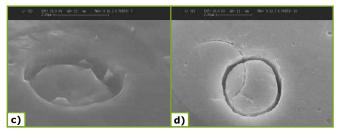

Great care is also taken for the pressure application so as to achieve an assembly with uniform height and to obtain hermetic cavities. Optical observations of the ring, shown in figure 17, are also performed after assembly.

Figure 17 - Optical observation of the ring after assembly a) and after lid removal b).

These observations show that indium is uniformly spread around the UBM which indicates that the pressure is applied

uniformly, enhancing the chances of having a hermetic assembly.

Both quartz and pyrex samples are tested and no differences are observed. Since most pyrex samples are used for the gold tin assembly, we mainly use quartz samples. 11 such samples, with ring width from  $60\mu m$  to  $105\mu m$ , are achieved using the optimized assembly conditions and tested under the same fine leak conditions as explained previously. The cavity to test these samples is generally made after assembly except for a few samples.

The results are shown in table 3:

| Sample | Process      | Leak rate<br>mbar I/s  |

|--------|--------------|------------------------|

| 1      | 125°C - 300S | < 10 <sup>-8</sup>     |

| 2      | 125°C - 300S | < 10 <sup>-8</sup>     |

| 3      | 125°C - 300S | < 2.10 <sup>-9</sup>   |

| 4      | 125°C - 300S | < 1,2.10 <sup>-8</sup> |

| 5      | 125°C - 300S | < 2,6.10 <sup>-8</sup> |

| 6      | 125°C - 300S | < 3.10-8               |

| 7      | 125°C - 300S | < 5.10 <sup>-9</sup>   |

| 8      | 125°C - 300S | < 1,5 10-8             |

| 9      | 125°C - 300S | < 1,2 10-8             |

| 10     | 125°C - 300S | < 1,1 10-8             |

| 11     | 125°C - 300S | < 1,2 10 <sup>-8</sup> |

Table 3 - He Leak rate results with Indium ring.

All samples are within spec which is an excellent result. In addition, these assemblies proved to be robust as the hole for leak rate testing is made after assembly which may induces large mechanical stresses on the ring, however it does not seem to influence the result. Again, no influence of the ring geometry is observed.

### **RELIABILITY TESTS**

As indium is not a standard solder used for hermetic sealing, some fatigue tests are performed on the samples. They are subjected to thermal shocks as described below:

- Immersion under 0°C water followed by immersion under 100°C water

- -40°C to +85°C at 10°C/min with 10 min plateau.

The results of these tests are shown in table 4 and figure 18:

| Sample | Leak rate before shock mbar I/s | Leak rate after 20 shocks mbar I/s |

|--------|---------------------------------|------------------------------------|

| 1      | < 1,5 10-8                      | 2.10-8                             |

| 2      | < 1,2 10-8                      | 2.2.10-8                           |

| 8      | < 1,1 10-8                      | 1.1.10-8                           |

| 9      | < 1,2 10-8                      | 1.5.10-8                           |

| 10     | <10-8                           | 1.6.10-8                           |

| 11     | <10-8                           | 2.4.10-8                           |

Table 4 - Leak rate measured after thermal shock.

Again these results are excellent as there is almost no modification of the leak rate before and after the test. It is very promising and shows the robustness of the seal considering the CTE mismatch between the silicon substrates and the quartz lids. Some heights measurements of the ring are also done and no significant evolution is seen. Indium proves to be a good reliable sealing solder, and a robust assembly method is defined here.

### Leak Rate Evolution after 500 Thermal Cycles (-40/+85°C)

Figure 18 - Evolution of the leak rate after 500 cycling from -40 to +85°C.

### **CONCLUSIONS**

A fluxless sealing method using either AuSn20 or Indium is demonstrated. It achieves hermetic bonding using ring as thin as 60µm wide and a batch deposition process. Two reliable hermetic bonding processes are defined: a reflow compression for AuSn20 and a thermocompression for Indium. In both cases a batch process is demonstrated: The reflow process may be implemented on a full wafer level under a controlled atmosphere and the assembly process using low pressure may be achieved by groups of substrates under a compression arm.

Indium is found to be a very reliable sealing solder passing the hermetic norm 1014 of the MIL-STD-883<sup>E</sup>, before and after thermal shocks for all assemblies. It also proved to be more flexible than AuSn20 as it handles CTE mismatch.

In a next step some active samples should be made with lasers and photodiodes encapsulated in ceramic lid for examples. The assembly parameters could be refined and the necessity of stoppers investigated. This sealing method seems suitable for MEMS devices as the ring could be designed around the active moving part. The solder should be chosen depending on the temperature limitations, the applications and the thermal stresses.

### **ACKNOWLEDGMENTS**

The Authors would like to thank Intexys photonics which partially financed this study as well as the European project ODIN. The ODIN project has been labeled as a PIDEA+ project. PIDEA is the acronym of Packaging and Interconnection Development for European Applications. Swedish and French partners have been respectively funded by VINNOVA (Swedish Governmental Agency for Innovation Systems) and the ministère français de l'industrie (French Governmental Agency).

### **REFERENCES**

- [1] C.G.M. Vreeburg and C.M. Groeneveld, "Packaging Trends for semiconductors Lasers for DWDM-applications", 49th Proceedings of the ECTC, June 1999, pp. 1-4.

- [2] Y.S. Bang, J.M. Kim, Y. Kim, J.M. Kim, Y.K Kim, "Fabrication and Characterization of RF MEMS Package Based on LTCC Lid Substrate and Gold-Tin Eutectic Bonding", Solid-State Sensors, Actuators and Microsystems Conference, June 2007, pp 2115-2118.

- [3] G. Elger, L. Shiv, C. Ching-Hua, A. Kilian, A. Hase, M. Hescel, J. Kuhmann, "A fluxfree soldering process for local hermetic sealing of optoelectronic subassemblies", hymite, ITG-Workshop, May 2003.

- [4] C. Kopp et al., "Merging parallel optics packaging and surface mount technologies", Proceedings of the SPIE, San Jose, Ca, January 2008, Vol. 6899, pp. 68990Y¬68990Y-8.

- [5] http://www.reinhardt-microtech.ch.

- [6] M. Fendler, M. Volpert, F. Marion, L. Mathieu, J.-M. Debono, P. Castelein, C. Louis, "Ultra fine pitch hybridization of large imaging detectors", IEEE-Nuclear¬Science-Symposium conference, October 2003, Vol. 5, pp. 3518-21.

- [7] M. Hutter, M. von Suchodoletz, H. Oppermann, G. Engelmann, O. Ehrmann, H. Reichl, "Electroplated AuSn Solder for Flip Chip Assembly and Hermetic Sealing",7th VLSI-PKG-WS, Nov. 2004.

- [8] R.R. Chromik, D-N. Wang, A. Shugar, L. Limata, M.R. Notis, and R.P. Vinci, "Mechanical properties of intermetallic compounds in the Au-Sn system", J. Mater. Res., Aug 2005, Vol. 20, N°8, pp. 2161-2172.

- [9] M. Hutter, F. Hohnke, H. Oppermann, M. Klein, G. Engelmann, "Assembly and Reliability of Flip Chip Solder Joints Using Miniaturised Au/Sn Bumps", 54th Proceedings of ECTC, June 2004, Vol. 1, pp. 49-57.

- [10] S. Bonafede, A. Huffman, W. Devereux Palmer, "Layer Structure and Thickness Effects on Electroplated AuSn Solder Bump Composition", IEEE transact. On components and packaging techno, Sept. 2006, vol. 29, N°3, pp. 604-609.

- [11] http://www.set-sas.fr.

- [12] Gilbert Lecarpentier, Jean Stephane Mottet, Francois Marion, "Wafer Level Packaging Chip to Wafer approach using Flux Less Soldering and featuring Hermetic Seal Capability", IMAPS, 4th Annual Conference on Device Packaging, Scottsdale, Arizona, March 2008.

- [13] Jane E. Jellison, « Gold-Indium Intermetallic Compounds Properties and Growth Rates", Material Control and Applications Branch, 8 November 1979, NASA report.

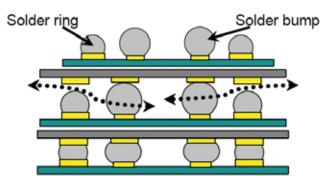

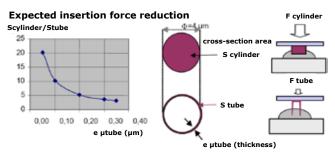

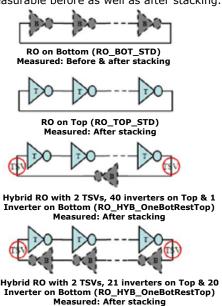

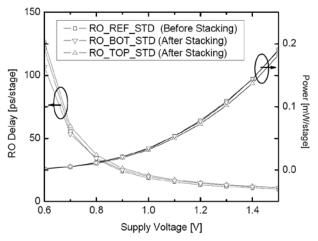

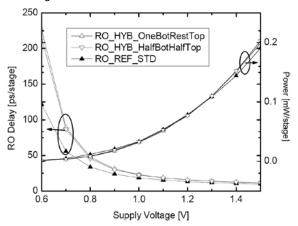

### **ABSTRACT**

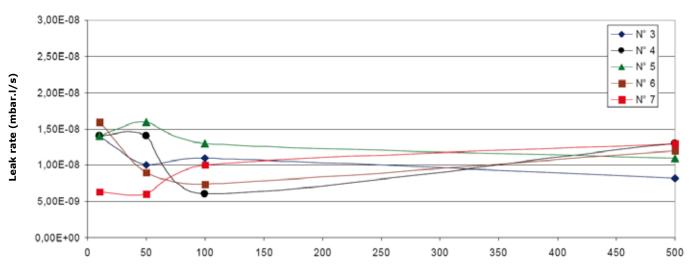

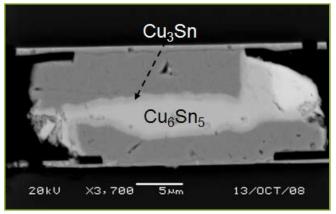

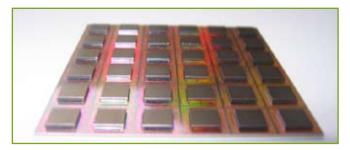

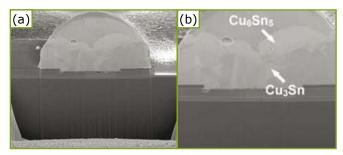

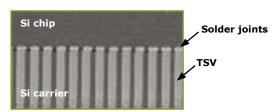

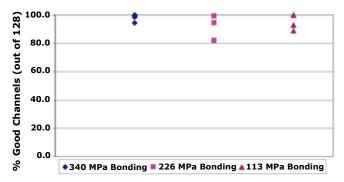

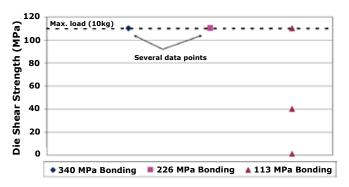

3D die stacking is a key technology for enabling 3D integration wherein two or more dies are stacked on top of each other with vertical interconnections. This result in high speed interconnects with reduced noise and crosstalk as compared to wire bonded assemblies. 3D integration may require sequential stacking of multiple dies without disturbing the previously bonded die. This can be achieved by transient liquid phase (TLP) bonding where the melting point of the intermetallic formed after the bonding is much higher than that of the solder itself. In this paper, we demonstrate the feasibility of narrow pitch TLP bonding for the Cu-Sn system in die stacking applications. Furthermore, we explore several process options for cost reduction, throughput enhancement and thermal budget minimization. More than 90% yielding devices are achieved on 40µm pitch peripheral array and 100µm pitch area array dies at 250°C using both flux and No flow UnderFill (NUF) using both die-to-die and die-to-wafer setup. Preliminary bonding results at temperature less than 200°C are also presented.

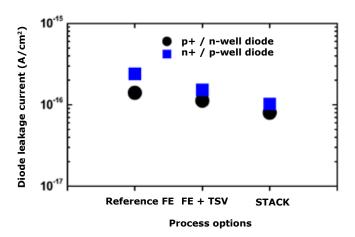

### **INTRODUCTION**

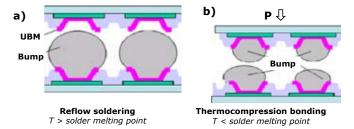

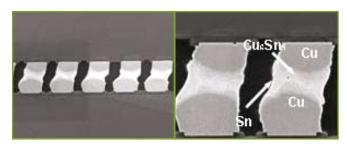

At IMEC, along with direct Cu-Cu bonding [1], low temperature alternatives for die stacking are being explored. Transient liquid phase (TLP) bonding is a very attractive process for the realization of vertical interconnection between devices. TLP bonding is a relatively low temperature thermo-compression type bonding process that transforms solder into high melting point intermetallic (IMC) bonds [2,3] (an alternative name of solid liquid interdiffusion is sometimes used for what is fundamentally the same process) [4,5]. Such process enables repeated stacking of additional layers without remelting the bumps at lower levels of the stack. In this way, TLP bumping facilitates multi-level 3D interconnects, and hence recently drew much attention in 3D chip stacking technology [6-8].

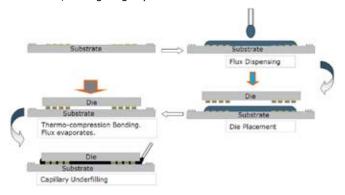

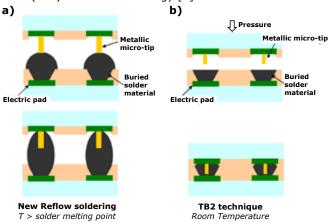

In this paper, we demonstrate the feasibility of narrow pitch TLP bonding for the Cu-Sn system in die stacking applications. Furthermore, we explore several process options for cost reduction, throughput enhancement and thermal budget minimization. Cost reduction is achieved by reducing the number of process steps required by using no flow underfill (NUF) [8,9] during the bonding instead of flux. No underfilling is required on the samples bonded with NUF thereby eliminating the extra processing steps required during capillary underfilling process. Throughput enhancement is achieved by doing die to wafer bonding instead of die to die bonding. Further lowering of the bonding temperature may be necessary for specific applications such as DRAM memory. Cu-Sn bonding process at temperatures below 200°C has been explored for this reason.

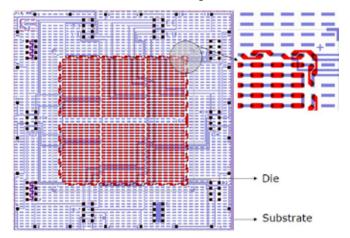

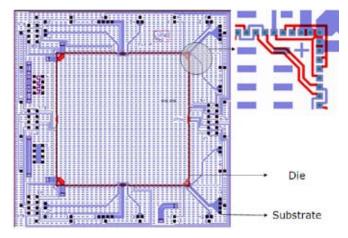

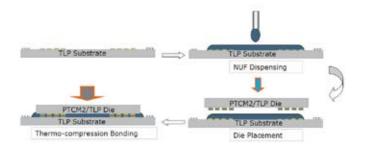

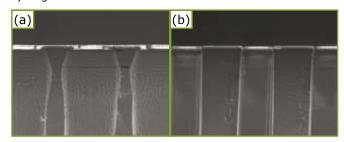

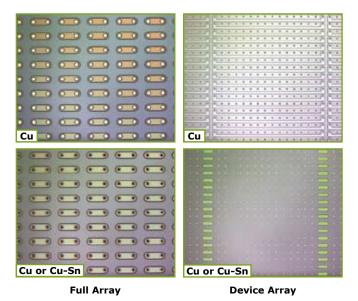

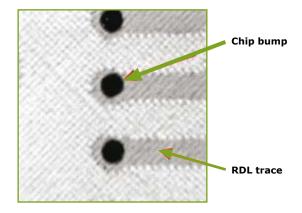

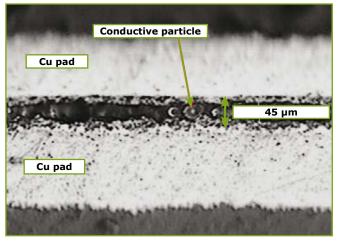

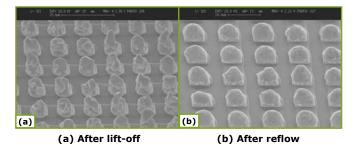

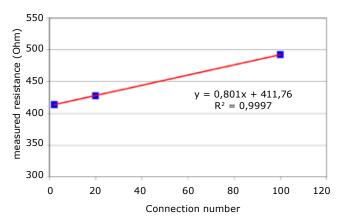

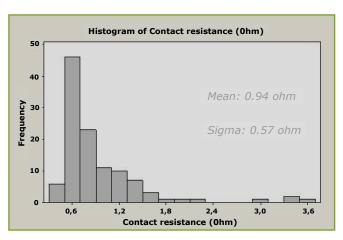

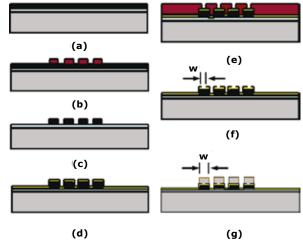

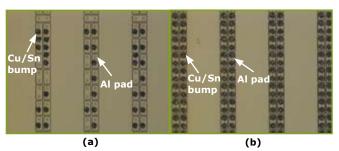

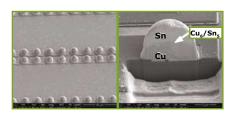

### **TEST SAMPLE FABRICATION**

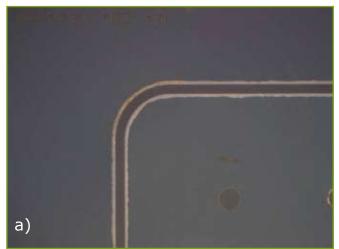

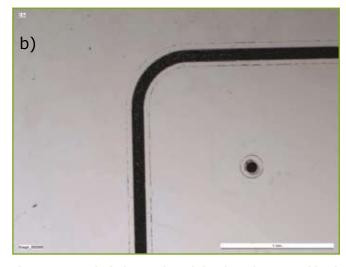

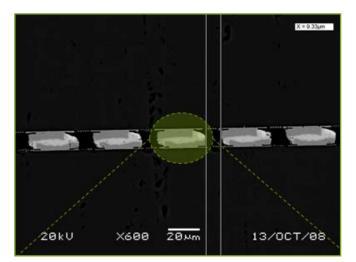

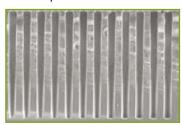

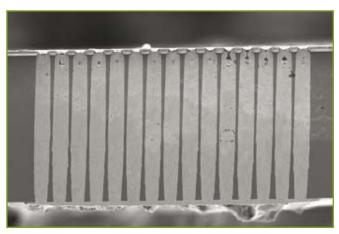

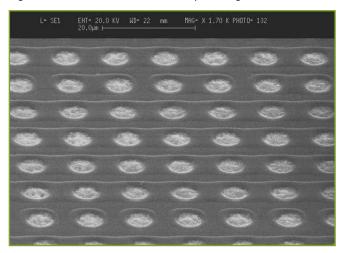

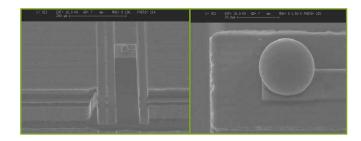

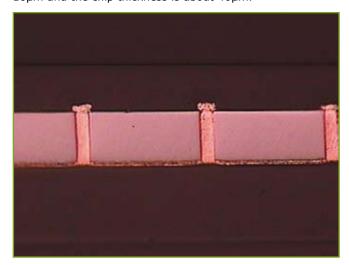

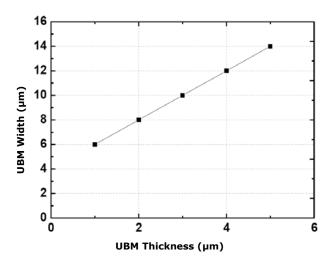

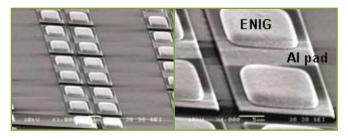

The test samples are designed so that after the bonding the dies are connected into a daisy chain to measure the electrical yield of the bonding process. Die to die bonding and die to wafer placement is performed on a **SET FC150 flip-chip bonder** and collective bonding is performed on a wafer bonding tool or on the flip-chip bonder with a modified pickup tool. Two different sets of 200mm wafers are processed to form top die and landing die. 300nm single damascene Cu routing lines for the daisy chain connections are processed on both sets of wafers followed by a thin passivation layer on top of the Cu routing lines, which is patterned for electro-plating. The wafers are then bumped with Cu UBM on the landing substrate and Cu UBM and Sn bump on the die substrate.

For bumping the wafers, on the landing substrate Ti/Cu/Ti seed layer is sputter coated followed by lithography for bump electroplating. 5µm thick Cu is electroplated in Nexx Stratus 100 electroplater. Second lithography is performed to pattern Au bond pads for wire bonding. Finally the resist is stripped and seed layer etched to finish the processing on the landing substrate. The wafer is diced into 8x8mm dies for individual die bonding or 48x48mm 6x6 array of landing dies) for collective bonding.

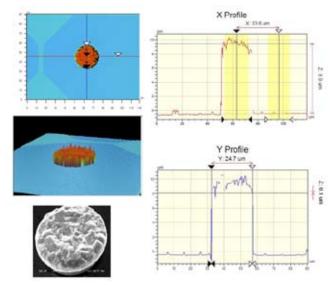

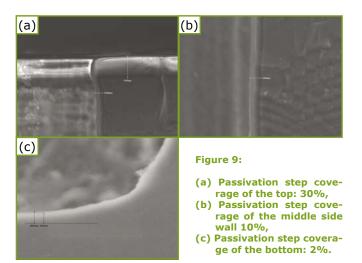

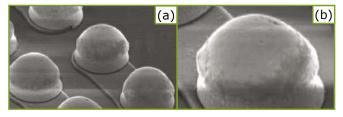

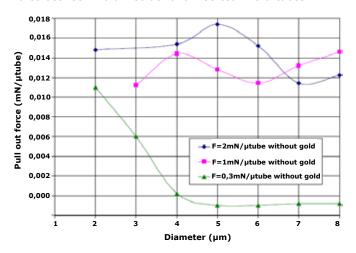

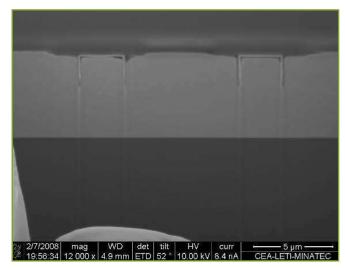

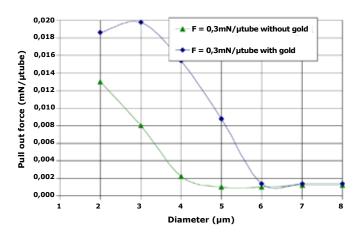

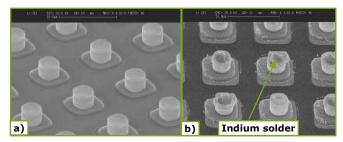

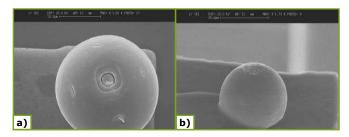

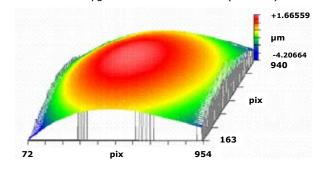

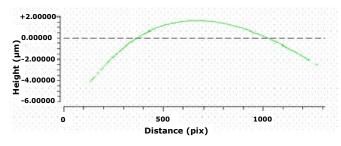

Figure 1 - Optical profilometer scan of the solder bumped die, showing the bump roughness.